# (12) United States Patent **Yajima**

# (54) SPIKE GENERATION CIRCUIT, INFORMATION PROCESSING CIRCUIT, POWER CONVERSION CIRCUIT. DETECTOR, AND ELECTRONIC CIRCUIT

(71) Applicant: JAPAN SCIENCE AND TECHNOLOGY AGENCY,

Kawaguchi (JP)

(72) Inventor: Takeaki Yajima, Tokyo (JP)

Assignee: JAPAN SCIENCE AND TECHNOLOGY AGENCY,

Kawaguchi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 17/408,599

Filed: Aug. 23, 2021

(65)**Prior Publication Data**

> US 2022/0014179 A1 Jan. 13, 2022

# Related U.S. Application Data

of application No. PCT/JP2020/006045, filed on Feb. 17, 2020.

### (30)Foreign Application Priority Data

Feb. 28, 2019 (JP) ...... JP2019-036951

(51) Int. Cl. H03K 3/00 H03K 3/02

(2006.01)(2006.01)

(Continued)

(52)U.S. Cl.

CPC ...... H03K 3/02 (2013.01); H03K 5/01 (2013.01); H03K 19/20 (2013.01); H03K 2005/00013 (2013.01)

### US 11.444.605 B2 (10) Patent No.:

(45) Date of Patent: Sep. 13, 2022

# Field of Classification Search

CPC ...... H03K 3/02; H03K 5/01; H03K 19/20; H03K 2005/00013

(Continued)

#### (56)References Cited

## U.S. PATENT DOCUMENTS

9/1998 Imamiya 5,812,001 A 6,242,988 B1\* 6/2001 Sarpeshkar ....... G06N 3/0635 331/111

(Continued)

## FOREIGN PATENT DOCUMENTS

8-242148 A JР 9-50051 A 2/1997 (Continued)

# OTHER PUBLICATIONS

International Search Report dated Apr. 14, 2020, issued in counterpart application No. PCT/JP2020/006045 (6 pages).

Primary Examiner — Ryan Jager (74) Attorney, Agent, or Firm — WHDA, LLP

#### **ABSTRACT** (57)

A spike generation circuit includes a first CMOS inverter connected between a first power supply and a second power supply, an output node of the first CMOS inverter being coupled to a first node that is an intermediate node coupled to an input terminal to which an input signal is input, a switch connected in series with the first CMOS inverter, between the first power supply and the second power supply, a first inverting circuit that outputs an inversion signal of a signal of the first node to a control terminal of the switch, and a delay circuit that delays the signal of the first node, outputs a delayed signal to an input node of the first CMOS inverter, and outputs an isolated output spike signal to an output terminal.

# 38 Claims, 86 Drawing Sheets

# US 11,444,605 B2

Page 2

| (51)                                                                        | Int. Cl.<br>H03K 5/01<br>H03K 19/20<br>H03K 5/00<br>Field of Clas | ssificatio | (2006.01)<br>(2006.01)<br>(2006.01)<br><b>n Search</b> |            | 2016/0<br>2019/0 |             | 12/2016<br>10/2019 | Schmiege      |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------|------------|--------------------------------------------------------|------------|------------------|-------------|--------------------|---------------|

| USPC                                                                        |                                                                   |            |                                                        |            |                  | EODEIG      | NI DATE            | NIT DOCUMENTS |

| See application file for complete search history.  FOREIGN PATENT DOCUMENTS |                                                                   |            |                                                        |            |                  |             |                    | NI DOCUMENTS  |

| (56)                                                                        | References Cited                                                  |            | JP                                                     |            | 588 A            | 12/1998     |                    |               |

| (56)                                                                        | References Cited                                                  |            |                                                        | JP         | 2000-106         |             | 4/2000             |               |

| II C DATE                                                                   |                                                                   | DATES IT   | EVE DOCED CEVEC                                        |            | JP               | 2001-148    | 3619 A             | 5/2001        |

|                                                                             | U.S                                                               | PALENT     | DOCUMENTS                                              |            | JP               | 2002-100    | 961 A              | 4/2002        |

|                                                                             |                                                                   |            |                                                        |            | JP               | 2006-243    | 8877 A             | 9/2006        |

|                                                                             | 8,975,935 B1*                                                     | 3/2015     | Yung                                                   | G06N 3/049 | JP               | 2012-044    | 1265 A             | 3/2012        |

|                                                                             |                                                                   |            |                                                        | 327/263    | JP               | 2014-523    | 3592 A             | 9/2014        |

|                                                                             | 8,996,431 B2*                                                     | 3/2015     | Cruz-Albrecht                                          | G06N 3/049 | JP               | 2019-022    | 2047 A             | 2/2019        |

|                                                                             |                                                                   |            |                                                        | 706/15     | WO               | 2011/030    | 0848 A1            | 3/2011        |

| 2013                                                                        | 3/0024409 A1*                                                     | 1/2013     | Hunzinger                                              | G06N 3/049 | WO               | 2018/100    | 790 A1             | 6/2018        |

|                                                                             |                                                                   |            | Č                                                      | 706/25     |                  |             |                    |               |

| 2014                                                                        | 4/0032460 A1                                                      | 1/2014     | Cruz-Albrecht et al.                                   |            | * cited          | by examiner |                    |               |

FIG. 1A

FIG. 1B

FIG. 2A

FIG. 2B

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 13A

FIG. 13B

FIG. 13C

FIG. 13D

FIG. 14A

FIG. 14B

FIG. 15A

FIG. 15B

FIG. 16A

FIG. 16B

FIG. 16C

FIG. 16D

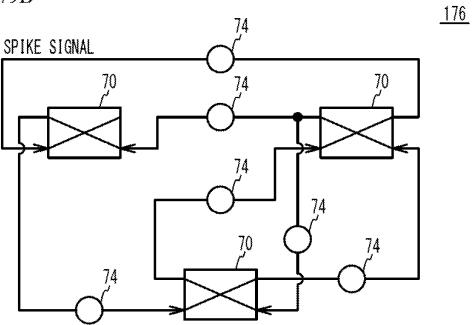

FIG. 17

FIG. 18

FIG. 19A

FIG. 20A

FIG. 20B

FIG. 21

FIG. 22A

FIG. 22B <u>137</u>

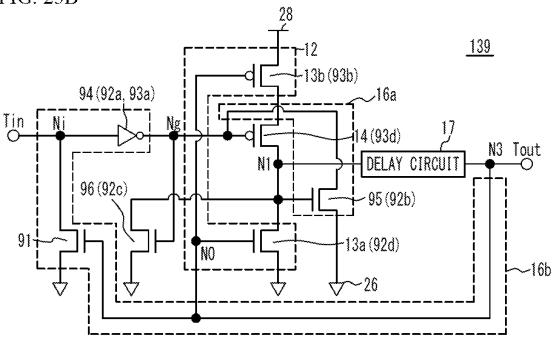

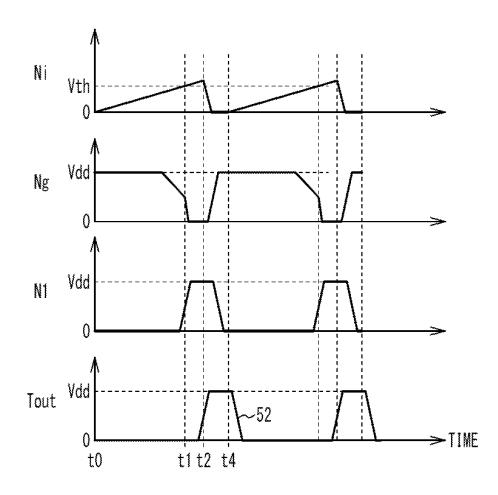

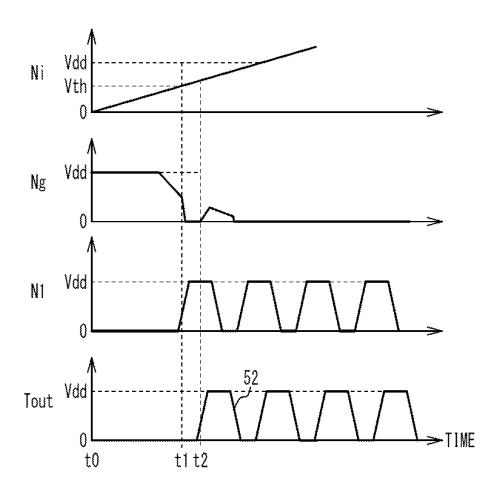

FIG. 23A

FIG. 23B

FIG. 24

FIG. 25

FIG. 26A

FIG. 27A

FIG. 27B

FIG. 28A

FIG. 28B 145 ~99 12 ~16a 94a 17 Tin N3 Tout -96 NI DELAY CIRCUIT Ng2 -14 -13a 91-~16b 94b

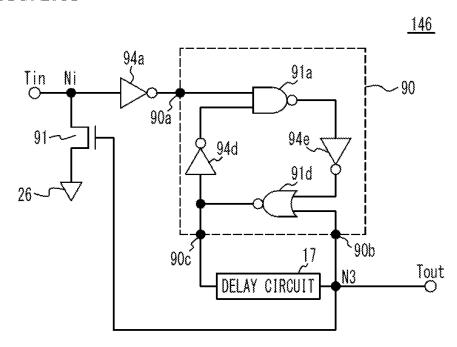

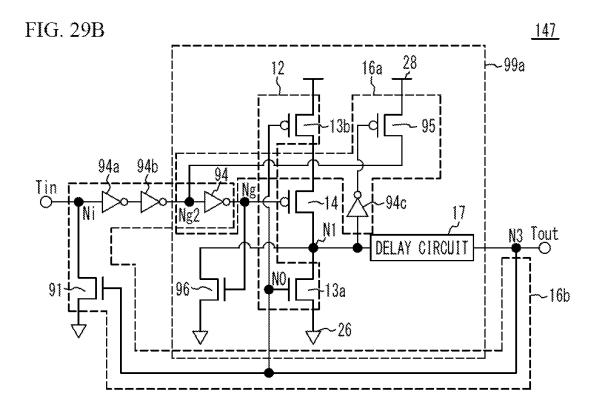

FIG. 29A

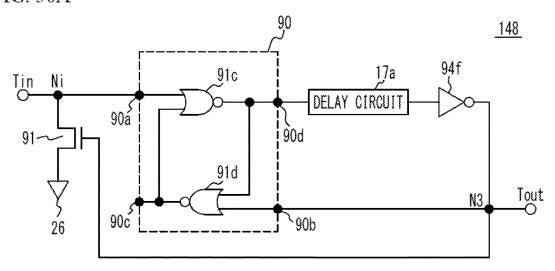

FIG. 30A

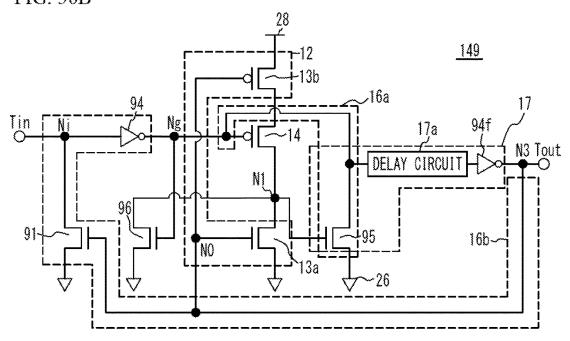

FIG. 30B

FIG. 31

FIG. 34A

FIG. 34B

FIG. 35

FIG. 36A

FIG. 36B

FIG. 37

6.0

S က

5.0

FIG. 38A

FIG. 39

FIG. 41

FIG. 42A

FIG. 42B

FIG. 43A

FIG. 43B

FIG. 43C

FIG. 44

FIG. 45

FIG. 46A

FIG. 46B

FIG. 46C

FIG. 47A

FIG. 47B

FIG. 47C

FIG. 48

FIG. 49

FIG. 50

FIG. 51A

FIG. 51B

FIG. 51C

FIG. 53

FIG. 55A

FIG. 55B

FIG. 55C

FIG. 57

FIG. 58

FIG. 60A

FIG. 60B

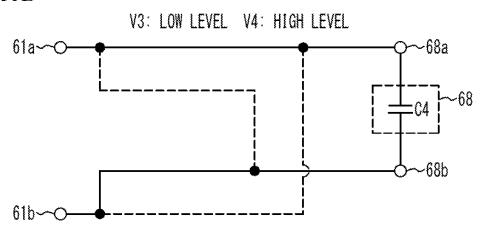

## FIG. 61A

FIG. 61B

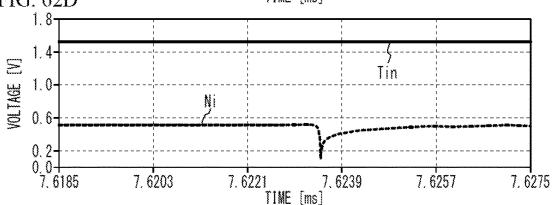

FIG. 62C

FIG. 62D

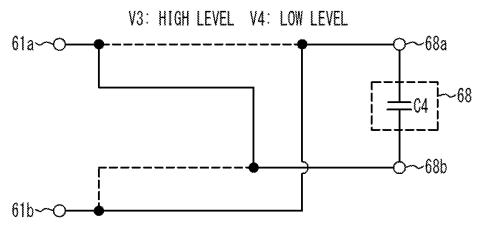

FIG. 63A

TIME [ms]

FIG. 64A

FIG. 64B

FIG. 64C

FIG. 65

FIG. 66A

## FIG. 67B

## FIG. 67C

FIG. 67D

FIG. 68A

FIG. 70A

FIG. 70B

FIG. 71

FIG. 72A

FIG. 73

FIG. 74

FIG. 75

FIG. 76

# FIG. 77A

FIG. 78A

Sep. 13, 2022

FIG. 78B

0

~52

t58

→TIME

FIG. 78C

FIG. 79A

<u>175</u>

# FIG. 80A

# FIG. 80B

# FIG. 81A

FIG. 82A

FIG. 82B

FIG. 82C

FIG. 83A

FIG. 83B

FIG. 84A

FIG. 84B

FIG. 85A

Sep. 13, 2022

FIG. 85B

FIG. 85C

FIG. 85D

FIG. 86

## SPIKE GENERATION CIRCUIT, INFORMATION PROCESSING CIRCUIT. POWER CONVERSION CIRCUIT, DETECTOR, AND ELECTRONIC CIRCUIT

## CROSS-REFERENCE TO RELATED APPLICATION

This application is based upon and claims the benefit of priority of the prior International Patent Application No. PCT/JP2020/006045, filed on Feb. 17, 2020, which claims the benefit of priority of Japanese Patent Application No. 2019-036951 filed on Feb. 28, 2019, the entire contents of which are incorporated herein by reference.

### TECHNICAL FIELD

A certain aspect of embodiments described herein relates to a spike generation circuit, an information processing tronic circuit.

### BACKGROUND ART

Spike generator circuits such as neuron circuits used in 25 neural networks have been known as disclosed in, for example, Japanese Patent Application Publication Nos. 2001-148619 and 2006-243877 and International Publication No. 2018/100790. Circuits in which a plurality of inverters are connected in multiple stages have been known 30 as disclosed in, for example, Japanese Patent Application Publication Nos. 2012-44265, H8-242148, 2000-106521.

#### SUMMARY

According to an aspect of the present disclosure, there is provided a spike generation circuit including: a first CMOS inverter connected between a first power supply and a second power supply, an output node of the first CMOS inverter being coupled to a first node that is an intermediate 40 node coupled to an input terminal to which an input signal is input; a switch connected in series with the first CMOS inverter, between the first power supply and the second power supply; a first inverting circuit that outputs an inversion signal of a signal of the first node to a control terminal 45 of the switch; and a delay circuit that delays the signal of the first node, outputs a delayed signal to an input node of the first CMOS inverter, and outputs an isolated output spike signal to an output terminal.

In the above configuration, the first inverting circuit may 50 be configured to output the inversion signal of the signal of the first node to the control terminal of the switch and a second node, and the delay circuit may include the first inverting circuit, and a second inverting circuit configured to output an inversion signal of a signal of the second node to 55 the input node of the first CMOS inverter and a third node coupled to the output terminal.

In the above configuration, the first inverting circuit may include an odd number of second CMOS inverters connected in a single stage or multiple stages between the first 60 node and the second node, input nodes of the odd number of second CMOS inverters being coupled to the first node, output nodes of the odd number of second CMOS inverters being coupled to the second node, and the second inverting circuit may include an odd number of third CMOS inverters 65 connected in a single stage or multiple stages between the second node and the third node, input nodes of the odd

2

number of third CMOS inverters being coupled to the second node, output nodes of the odd number of third CMOS inverters being coupled to the third node.

In the above configuration, the second inverting circuit may include three or more third CMOS inverters.

In the above configuration, a first capacitance element having a first end coupled to a fourth node and a second end coupled to a first reference potential terminal, the fourth node being between the three or more third CMOS inverters 10 may be provided.

In the above configuration, a capacitance value of the first capacitance element may be equal to or greater than a gate capacitance value of one FET in the three or more third CMOS inverters.

In the above configuration, a second capacitance element having a first end coupled to the first node and a second end coupled to a second reference potential terminal may be provided.

According to another aspect of the present disclosure, circuit, a power conversion circuit, a detector, and an elec- 20 there is provided a spike generation circuit including: a first CMOS inverter connected between a first power supply and a second power supply, an output node of the first CMOS inverter being coupled to a first node; a first switch connected in series with the first CMOS inverter, between the first power supply and the second power supply; an inverting circuit that outputs an inversion signal of a signal of the first node to a control terminal of the first switch; a delay circuit that delays the signal of the first node, outputs a delayed signal to an input node of the first CMOS inverter, and outputs an output spike signal to an output terminal; and an intermediate node provided in the inverting circuit and coupled to an input terminal to which an input signal is input.

In the above configuration, the first CMOS inverter may be configured to output a first level, which is one of a high level and a low level, and outputs a second level, which is the other of the high level and the low level, the first switch may be configured to be turned on when the first level is input to a control terminal, and turned off when the second level is input to the control terminal, the inverting circuit may include a first inverting circuit and a second inverting circuit, the first inverting circuit being configured to output the first level to the control terminal of the first switch when the first node changes from the first level to the second level, the second inverting circuit being configured to output the second level to the control terminal of the first switch when an output of the delay circuit becomes the second level, and the intermediate node may be provided in the second inverting circuit.

In the above configuration, the second inverting circuit may include a second switch that has a control terminal coupled to an output of the delay circuit and connects the intermediate node to a power supply, to which an initial level of the input signal is supplied, when the delay circuit outputs the second level.

In the above configuration, a second CMOS inverter having an input node coupled to the intermediate node and an output node coupled to the control terminal of the first switch may be provided.

In the above configuration, the first inverting circuit may include a third switch that has a control terminal coupled to the first node and connects the control terminal of the first switch to a power supply, to which the first level is supplied, when the first node becomes at the second level.

In the above configuration, a fourth switch that has a control terminal coupled to the control terminal of the first switch and connects the first node to a power supply, to

which the first level is supplied, when the control terminal of the first switch is at the second level may be provided.

In the above configuration, a voltage of the second power supply may be higher than a voltage of the first power supply, and the switch may be an N-channel transistor and 5 may be connected between the first node and the first power supply, or the switch may be a P-channel transistor and may be connected between the first node and the second power supply.

In the above configuration, a voltage conversion circuit 10 that outputs, to the intermediate node, a signal obtained by converting a voltage of the input signal may be provided, and the delay circuit may be configured not to output the output spike signal when the voltage of the input signal is within a predetermined range.

In the above configuration, a time constant circuit that increases a time constant of a rise of the input signal, and outputs a resulting signal to the intermediate node may be provided, and the delay circuit may be configured to output the output spike signal after a delay time relating to a time 20 constant of the time constant circuit after the input signal is input.

In the above configuration, an input circuit that increases or decreases a voltage of the intermediate node when an input spike signal is input as the input signal may be 25 provided, and the delay circuit may be configured to output the output spike signal when a frequency with which the input spike signal is input becomes within a predetermined range.

In the above configuration, an input circuit that varies a 30 voltage of the intermediate node according to an amount of change in the input signal with respect to time may be provided, and the delay circuit may be configured to output the output spike signal when the amount of change in the input signal with respect to time becomes within a predetermined range.

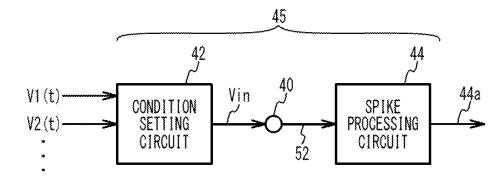

According to another aspect of the present disclosure, there is provided an information processing circuit including: the above spike generation circuit; a condition setting circuit that processes an input signal and outputs a processed 40 signal to the spike generation circuit to set a condition for the spike generation circuit to output spike signal; and a spike processing circuit that processes the output spike signal output by the spike generation circuit.

According to another aspect of the present disclosure, 45 be greater than a width of the output spike signal. According to another aspect of the present discovering to another aspect of the present dis

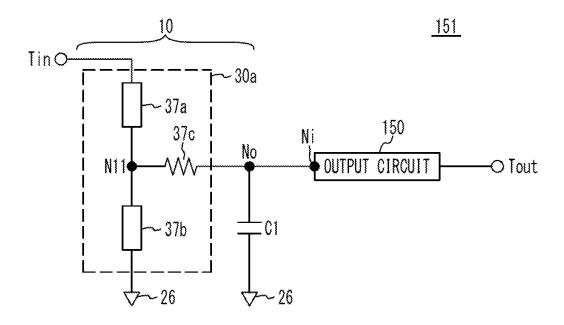

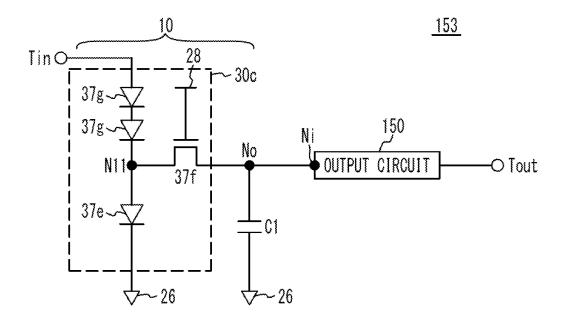

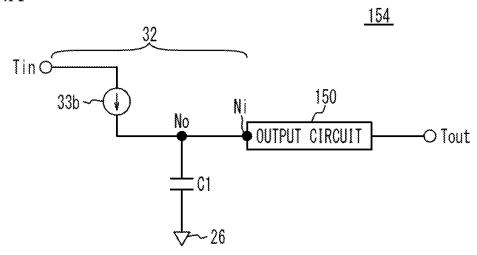

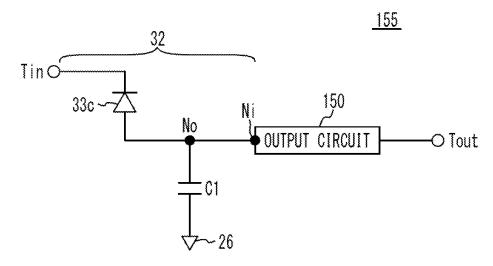

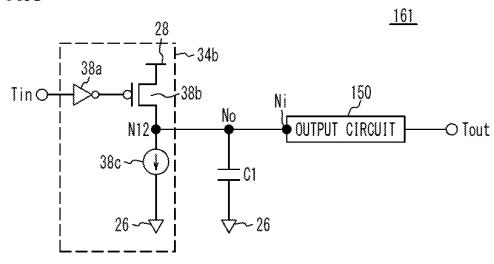

According to another aspect of the present disclosure, 50 there is provided a spike generation circuit including: a time constant circuit that increases a time constant of a rise of an input signal input to an input terminal, and outputs a resulting signal to an intermediate node from an output node; and an output circuit that outputs an isolated output spike signal to an output terminal and resets a voltage of the intermediate node in response to a voltage of the intermediate node becoming a threshold voltage, wherein the output circuit outputs the output spike signal after a delay time relating to a time constant of the time constant circuit after 60 the input signal is input.

In the above configuration, the time constant circuit may include: a capacitor having a first end coupled to the output node and a second end coupled to a first reference potential terminal, and a constant current element or constant current of circuit that has a first end coupled to the input terminal and a second end coupled to the output node, and generates a

4

constant current corresponding to a voltage difference between the first end and the second end.

In the above configuration, the constant current circuit may be a current mirror circuit including: a first transistor having a current input terminal and a current output terminal, one of the current input terminal and the current output terminal being coupled to the input terminal, the other of the current input terminal and the current output terminal being coupled to the output node, and a second transistor having a control terminal, a current input terminal, and a current output terminal, the control terminal being coupled to a control terminal of the first transistor, one of the current input terminal and the current output terminal being coupled to the input terminal through a first diode connected in a forward direction, the other of the current input terminal and the current output terminal being coupled to a second reference potential terminal through a second diode connected in a backward direction.

In the above configuration, the constant current element may be a diode connected in a backward direction or a transistor having a control terminal to which a voltage is applied so that the transistor is in an on-state.

According to another aspect of the present disclosure, there is provided a spike generation circuit including: a voltage conversion circuit that outputs, to an intermediate node, a signal obtained by converting a voltage of an input signal input to an input terminal; and an output circuit that outputs an isolated output spike signal to an output terminal and resets a voltage of the intermediate node in response to the voltage of the intermediate node becoming a threshold voltage, wherein the output circuit does not output the output spike signal when the voltage of the input signal is within a predetermined range.

In the above configuration, a capacitor having a first end coupled to the intermediate node and a second end coupled to a first reference potential terminal may be provided, and the voltage conversion circuit may include: a first element and a second element connected in series between the input terminal and a second reference potential terminal, and a resistance element having a first end coupled to a node, which is between the first element and the second element, and a second end coupled to the intermediate node.

In the above configuration, a product of a resistance value of the resistor and a capacitance value of the capacitor may be greater than a width of the output spike signal.

According to another aspect of the present disclosure, there is provided a spike generation circuit including: an input circuit that increases a voltage of an intermediate node by an amount corresponding to an input spike signal when the input spike signal is input to an input terminal, and/or decreases the voltage of the intermediate node by the amount corresponding to the input spike signal when the input spike signal is input to the input terminal; and an output circuit that outputs an isolated output spike signal to an output terminal and resets the voltage of the intermediate node in response to the voltage of the intermediate node becoming a threshold voltage, wherein the output circuit outputs the output spike signal when a frequency with which the input spike signal is input becomes within a predetermined range, and wherein the voltage of the intermediate node gradually decreases or increases over a time period longer than a width of the input spike signal during a time period when the input spike signal is not input to the input

According to another aspect of the present disclosure, there is provided a spike generation circuit including: an input circuit that increases a voltage of an intermediate node

by an amount corresponding to an input spike signal when the input spike signal is input to at least one of input terminals, and/or decreases the voltage of the intermediate node by the amount corresponding to a height of the input spike signal when the input spike signal is input to at least 5 one of the input terminals; and an output circuit that outputs an isolated output spike signal to an output terminal and resets the voltage of the intermediate node in response to the voltage of the intermediate node becoming a threshold voltage, wherein the output circuit outputs the output spike 10 signal when times at which the input spike signal is input to at least two of the input terminals is within a certain time period, and gradually decreases or increases the voltage of the intermediate node over a time period longer than a width of the input spike signal during a time period when no input 15 spike signal is input to the input terminals.

According to another aspect of the present disclosure, there is provided a spike generation circuit including: an input circuit that varies a voltage of an intermediate node according to an amount of change in an input signal input to an input terminal with respect to time; and an output circuit that outputs an isolated output spike signal to an output terminal and resets the voltage of the intermediate node in response to the voltage of the intermediate node becoming a threshold voltage, wherein the output circuit outputs the output spike signal when the amount of change in the input signal with respect to time becomes within a predetermine range.

#### BRIEF DESCRIPTION OF THE DRAWINGS

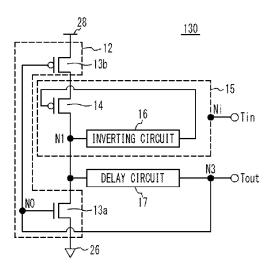

FIG. 1A and FIG. 1B are circuit diagrams of spike generation circuits in accordance with a first embodiment and a variation 1 thereof, respectively;

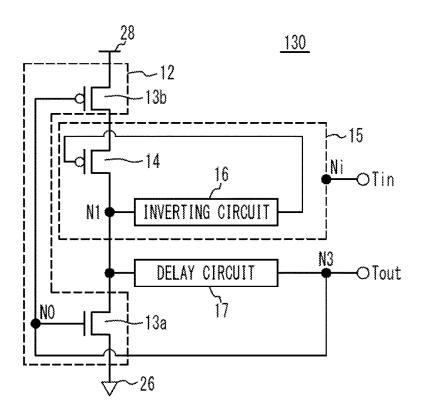

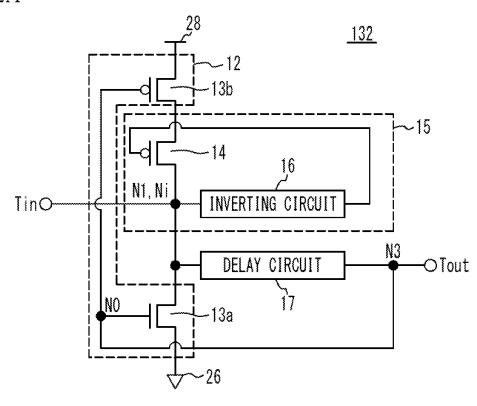

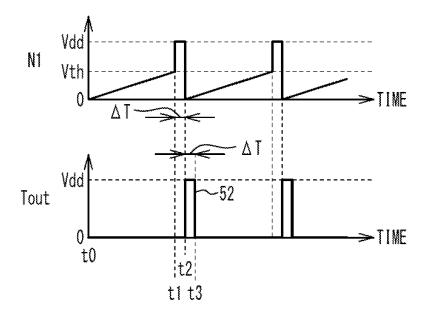

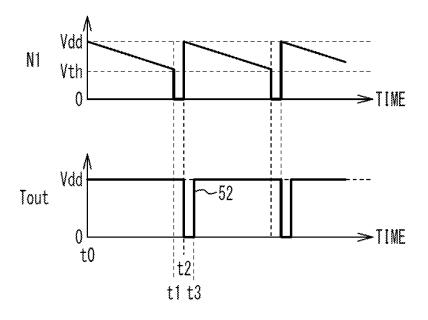

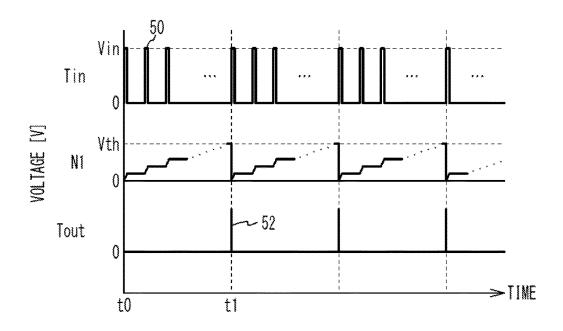

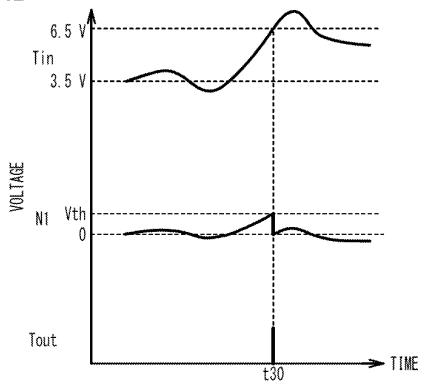

FIG. **2**A is a circuit diagram of a spike generation circuit 35 in accordance with a variation 2 of the first embodiment, and FIG. **2**B illustrates respective voltages of a node N1 and an output terminal Tout;

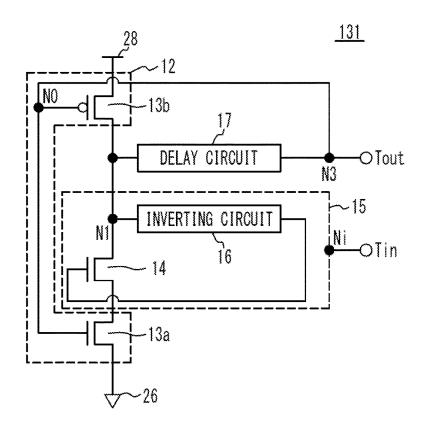

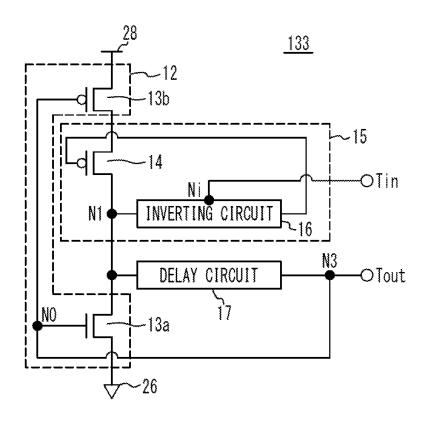

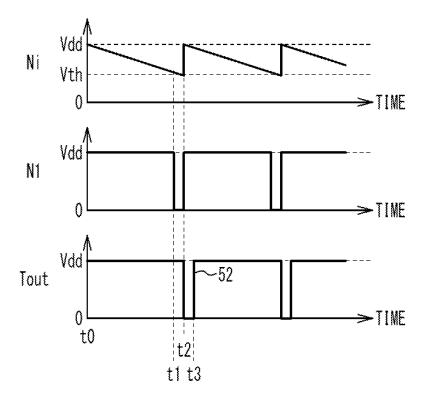

FIG. 3A is a circuit diagram of a spike generation circuit in accordance with a variation 3 of the first embodiment, and 40 fourth embodiment; FIG. 3B illustrates respective voltages of nodes Ni and N1 and the output terminal Tout; generation circuits i

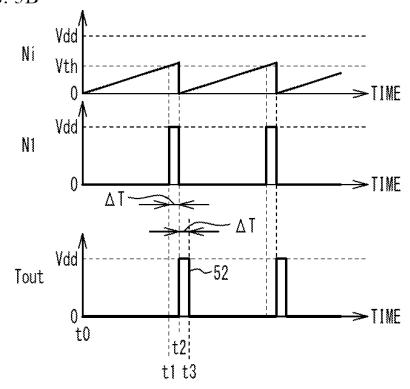

FIG. 4A is a circuit diagram of a spike generation circuit in accordance with a variation 4 of the first embodiment, and FIG. 4B illustrates respective voltages of the node N1 and 45 the output terminal Tout;

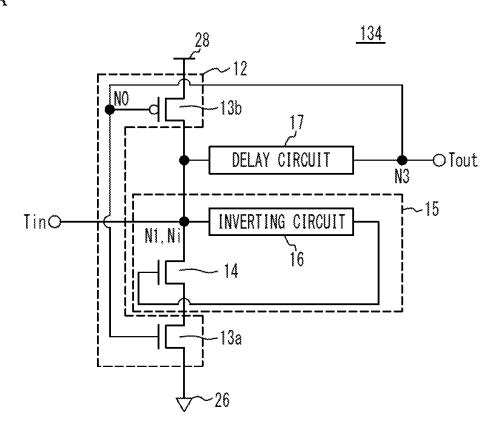

FIG. 5A is a circuit diagram of a spike generation circuit in accordance with a variation 5 of the first embodiment, and FIG. 5B illustrates respective voltages of the nodes Ni and N1 and the output terminal Tout;

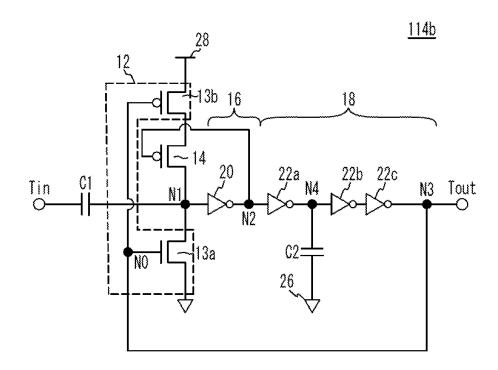

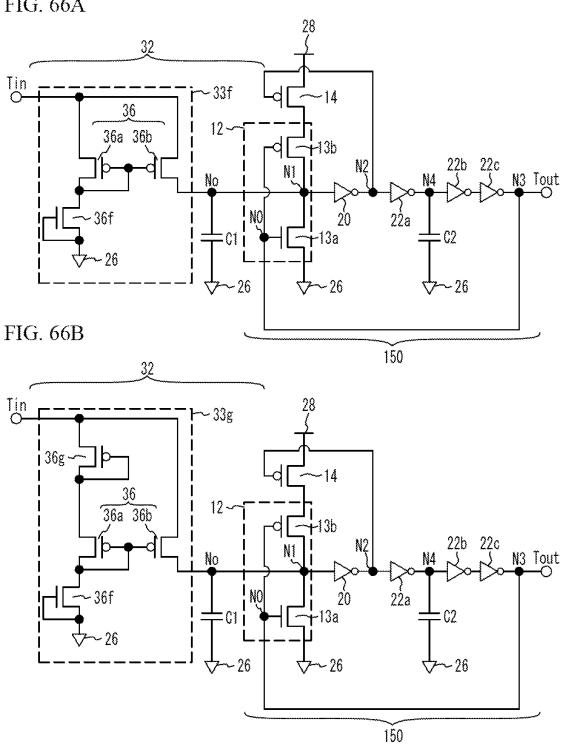

FIG. 6A is a circuit diagram of a spike generation circuit in accordance with a second embodiment, and FIG. 6B illustrates voltages with respect to time;

FIG. 7A is a circuit diagram of a spike generation circuit in accordance with a variation 1 of the second embodiment, 55 and FIG. 7B illustrates voltages with respect to time;

FIG. **8** is a circuit diagram of a spike generation circuit in accordance with a third embodiment;

FIG. 9A and FIG. 9B illustrate respective voltages of nodes with respect to time in the third embodiment;

FIG. 10A and FIG. 10B illustrate an input voltage, an output voltage, and a consumption current with respect to time in the third embodiment:

FIG. 11A to FIG. 11D illustrate the output voltage with respect to time in the third embodiment;

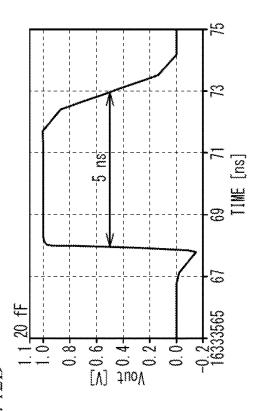

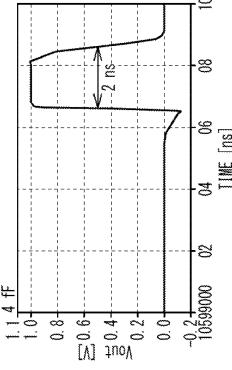

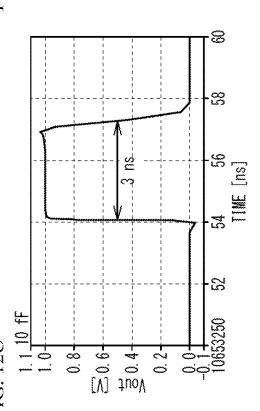

FIG. 12A to FIG. 12D illustrate the output voltage with respect to time in the third embodiment;

6

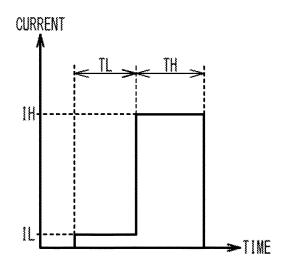

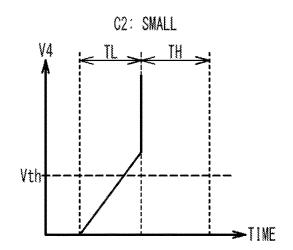

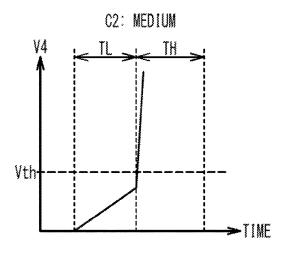

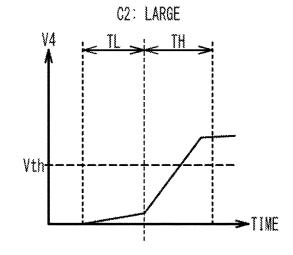

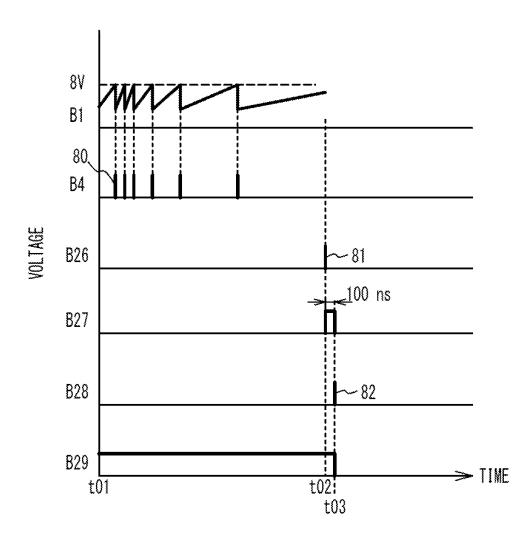

FIG. 13A to FIG. 13D are diagrams for describing the function of a capacitor C2;

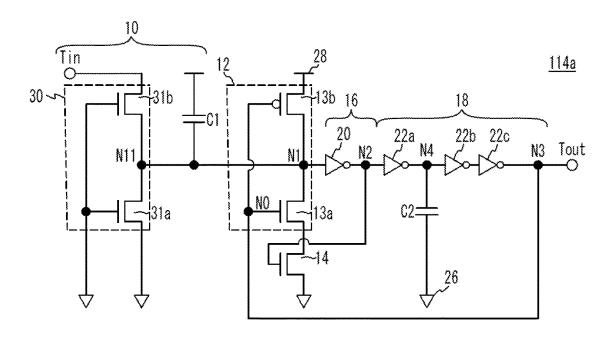

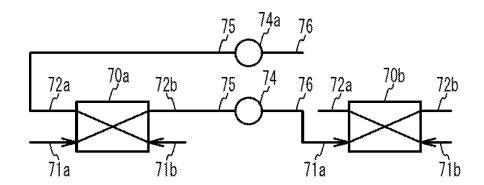

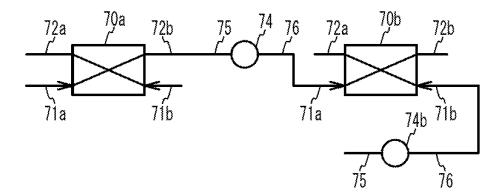

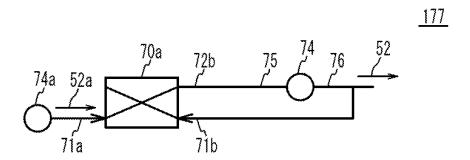

FIG. **14**A and FIG. **14**B are circuit diagrams of spike generation circuits in the third embodiment;

FIG. 15A and FIG. 15B are circuit diagrams of spike generation circuits in the third embodiment;

FIG. **16**A to FIG. **16**D illustrate the output voltage of the spike generation circuit with respect to time in the third embodiment;

FIG. 17 is a circuit diagram of a spike generation circuit of a variation 1 of the third embodiment;

FIG. 18 illustrates respective voltages of nodes with respect to time in the variation 1 of the third embodiment;

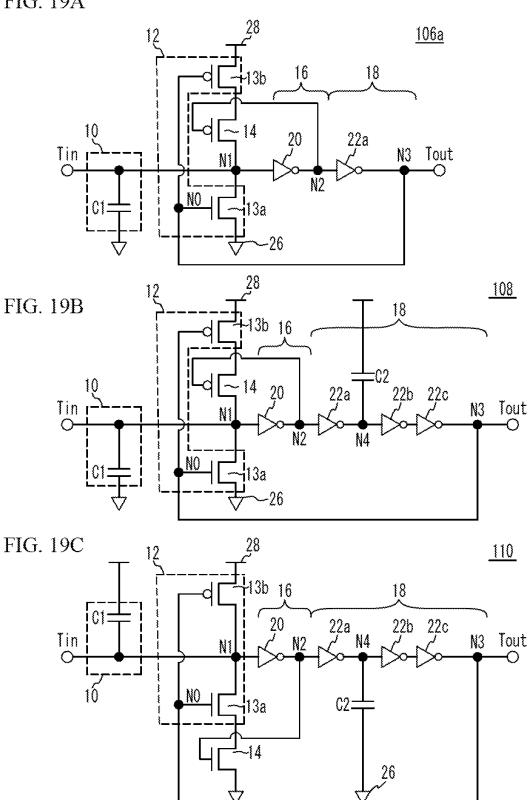

FIG. 19A is a circuit diagram illustrating another example of the spike generation circuit in accordance with the variation 1 of the third embodiment, and FIG. 19B and FIG. 19C are circuit diagrams of spike generation circuits in accordance with variations 2 and 3 of the third embodiment, respectively;

FIG. 20A and FIG. 20B illustrate respective voltages of nodes with respect to time in the variation 3 of the third embodiment:

FIG. 21 is a circuit diagram of a spike generation circuit in accordance with a variation 4 of the third embodiment;

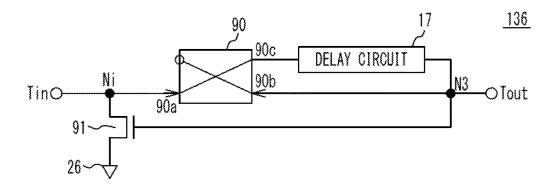

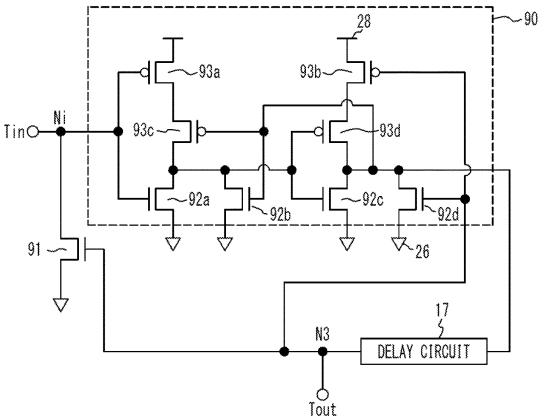

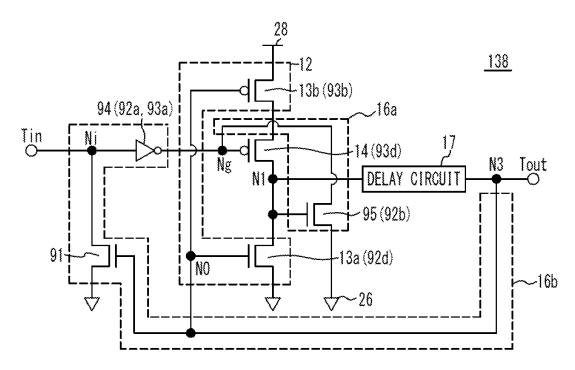

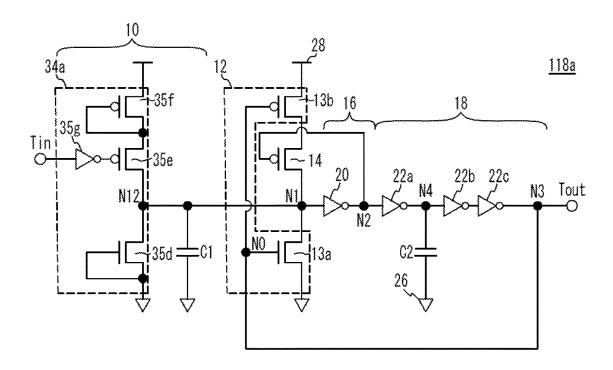

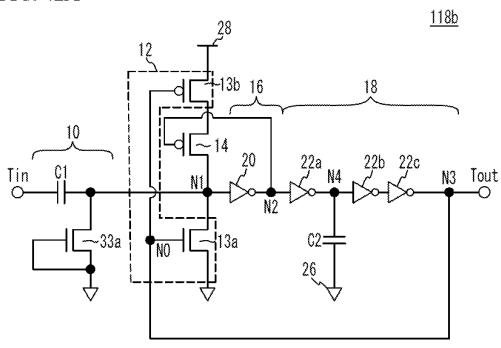

FIG. 22A and FIG. 22B are circuit diagrams of spike generation circuits in accordance with a fourth embodiment;

FIG. 23A and FIG. 23B are circuit diagrams of spike generation circuits in accordance with the fourth embodiment:

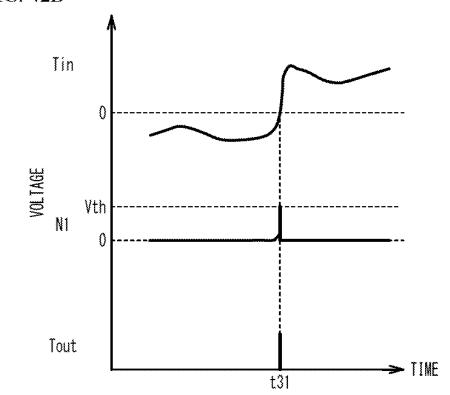

FIG. 24 illustrates respective voltages of a terminal and nodes with respect to time in the fourth embodiment;

FIG. **25** illustrates voltages with respect to time when no FET **91** is provided;

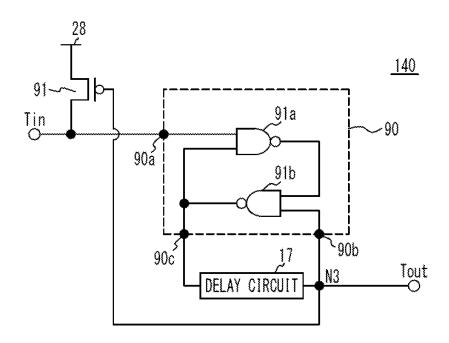

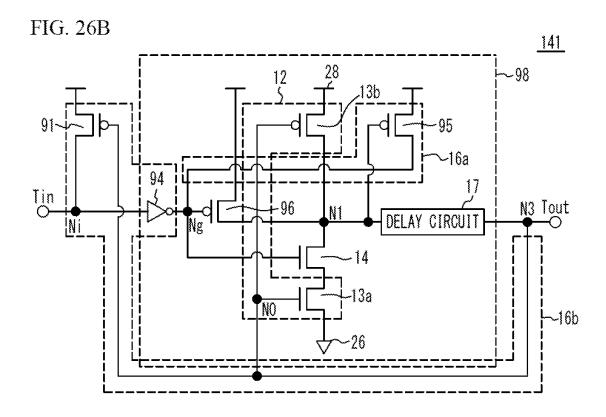

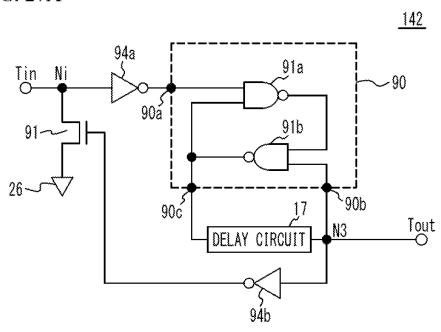

FIG. **26**Å and FIG. **26**B are circuit diagrams of spike generation circuits in accordance with a variation 1 of the fourth embodiment;

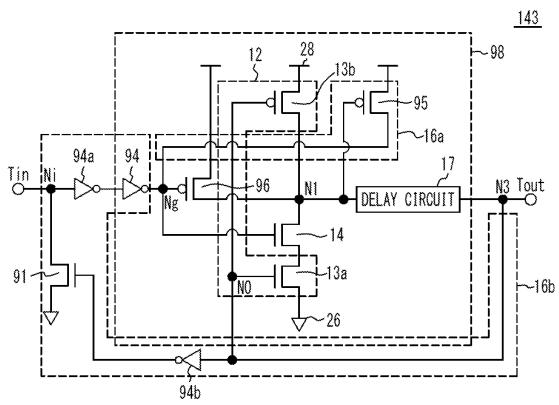

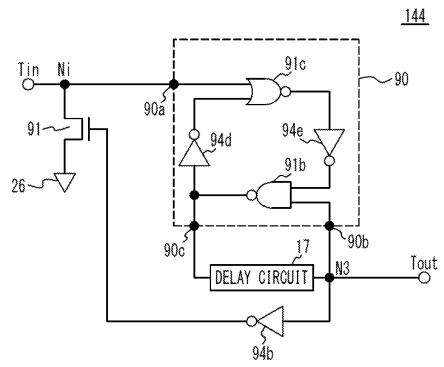

FIG. 27A and FIG. 27B are circuit diagrams of spike generation circuits in accordance with a variation 2 of the fourth embediment:

FIG. **28**A and FIG. **28**B are circuit diagrams of spike generation circuits in accordance with a variation 3 of the fourth embodiment;

FIG. **29**A and FIG. **29**B are circuit diagrams of spike generation circuits in accordance with a variation 4 of the fourth embodiment:

FIG. 30A and FIG. 30B are circuit diagrams of spike generation circuits in accordance with a variation 5 of the fourth embodiment;

FIG. 31 is a circuit diagram of a spike generation circuit in accordance with a fifth embodiment;

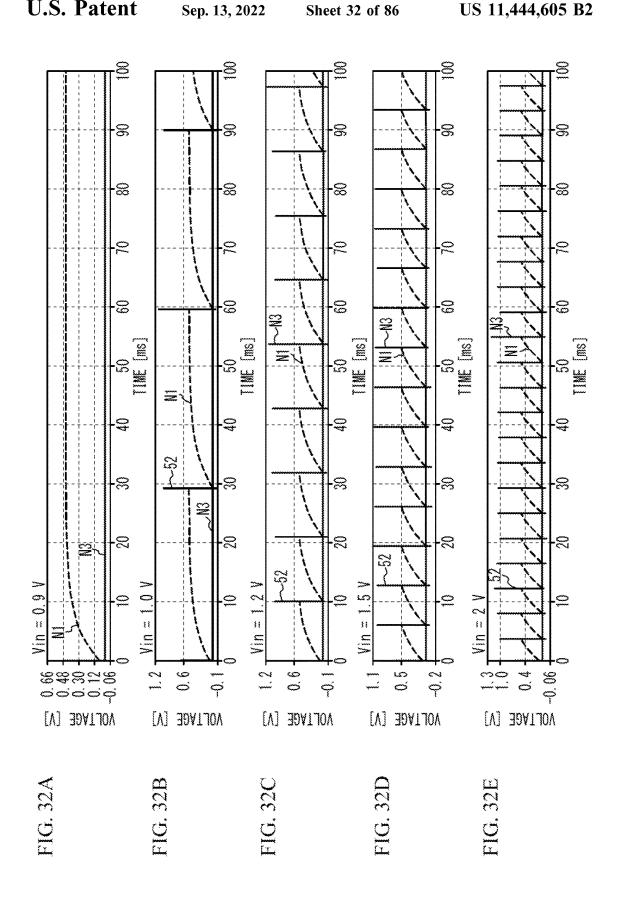

FIG. 32A to FIG. 32E illustrate the voltage of the node N1 and the output voltage with respect to time in the fifth embodiment;

FIG. 33A to FIG. 33D illustrate the voltage of the node N1 and the output voltage with respect to time in the fifth embodiment;

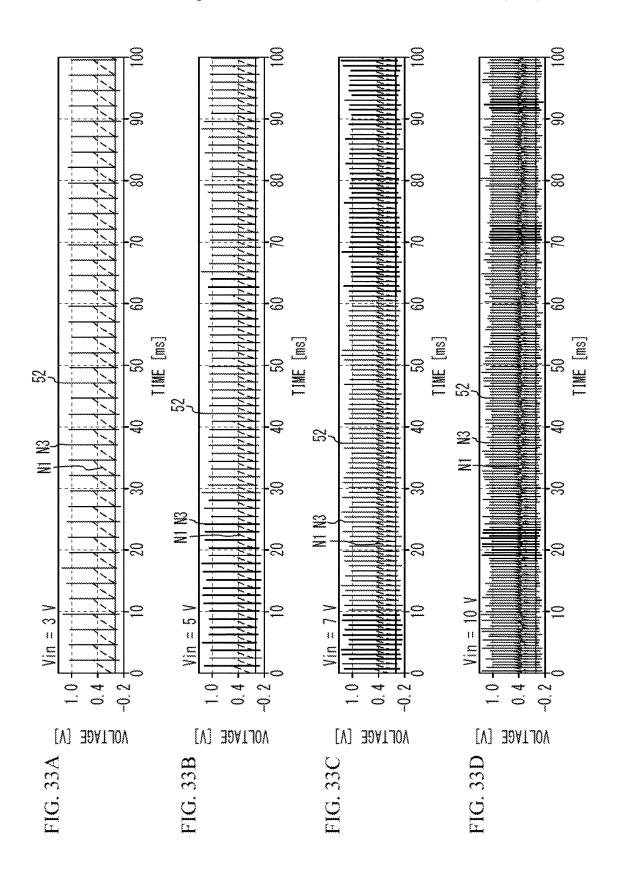

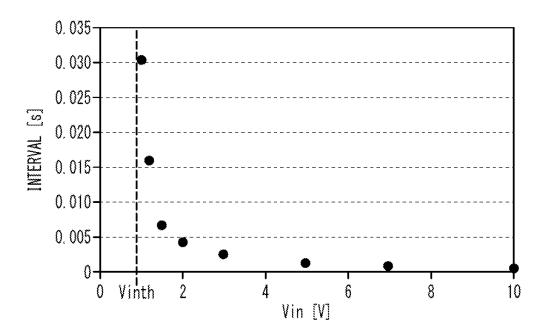

FIG. 34A illustrates frequency with respect to the input voltage in the fifth embodiment, and FIG. 34B illustrates an 60 interval with respect to the input voltage in the fifth embodiment.

FIG. 35 is a circuit diagram of a spike generation circuit in accordance with a variation 1 of the fifth embodiment;

FIG. **36**A is a circuit diagram of a spike generation circuit in accordance with a variation 2 of the fifth embodiment, and FIG. **36**B is a timing chart of the variation 2 of the fifth embodiment;

- FIG. 37 is a circuit diagram of a spike generation circuit in accordance with a variation 3 of the fifth embodiment;

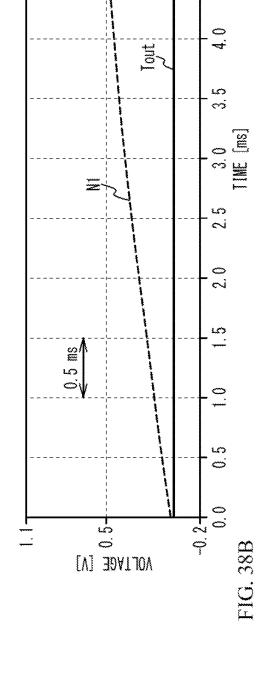

- FIG. 38A and FIG. 38B illustrate the voltage of the node N1 and the output voltage with respect to time in the variation 3 of the fifth embodiment;

- FIG. 39 is a circuit diagram of a spike generation circuit in accordance with a variation 4 of the fifth embodiment;

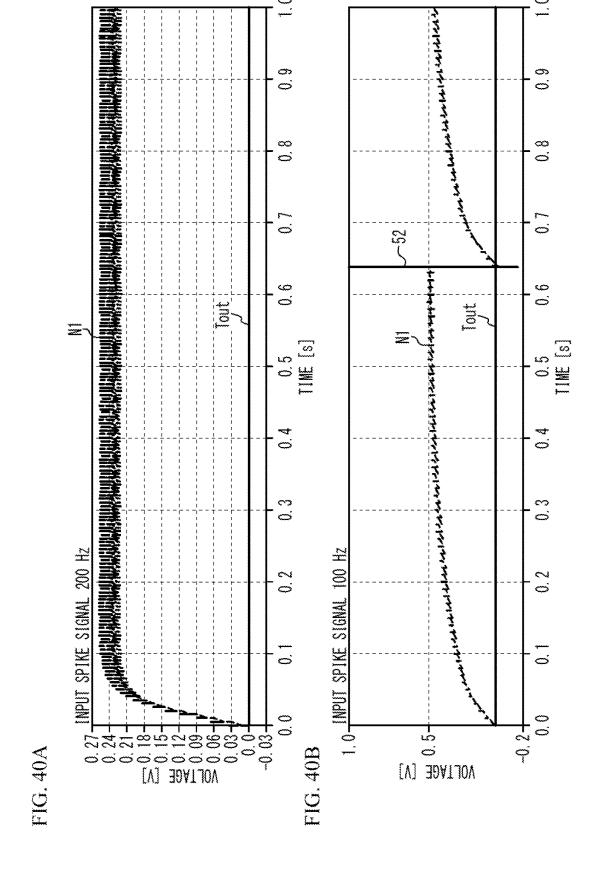

- FIG. 40A and FIG. 40B illustrate the voltage of the node N1 and the output voltage with respect to time in the variation 4 of the fifth embodiment;

- FIG. 41 is a circuit diagram of a spike generation circuit in accordance with a variation 5 of the fifth embodiment;

- FIG. **42**A is a circuit diagram of a spike generation circuit in accordance with a variation 6 of the fifth embodiment, and FIG. **42**B is a timing chart of the variation 6 of the fifth embodiment;

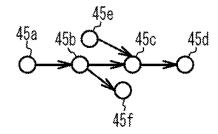

- FIG. **43**C are block diagrams of an information processing circuit in accordance with a sixth embodiment:

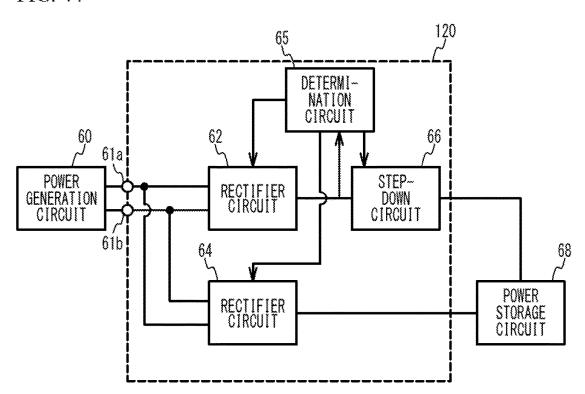

- FIG. 44 is a block diagram of a power conversion circuit in accordance with a seventh embodiment;

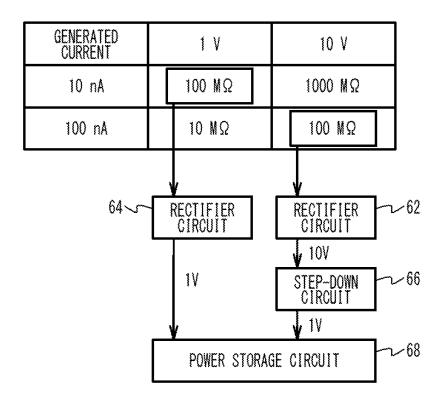

- FIG. **45** is a diagram for describing the operation of a determination circuit in the seventh embodiment;

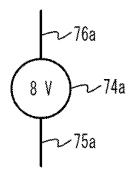

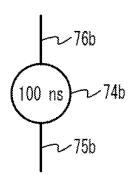

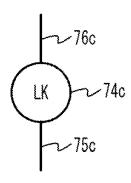

- FIG. 46A to FIG. 46C illustrate symbols in the spike  $^{25}$  generation circuits in the seventh embodiment;

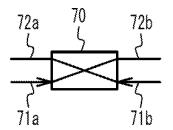

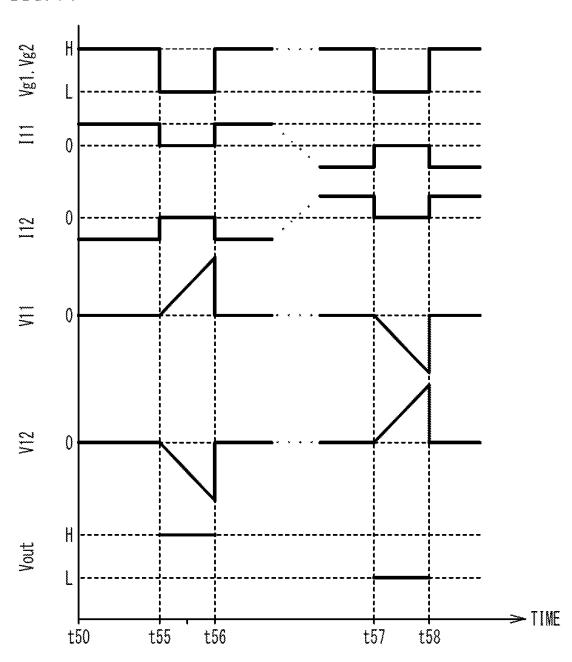

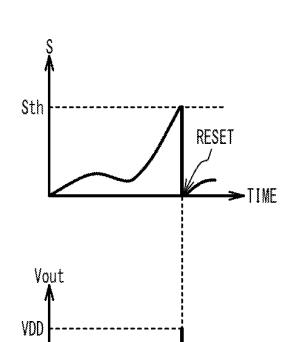

- FIG. 47A to FIG. 47C illustrate the operation of a flip-flop circuit in the seventh embodiment;

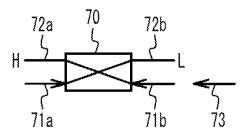

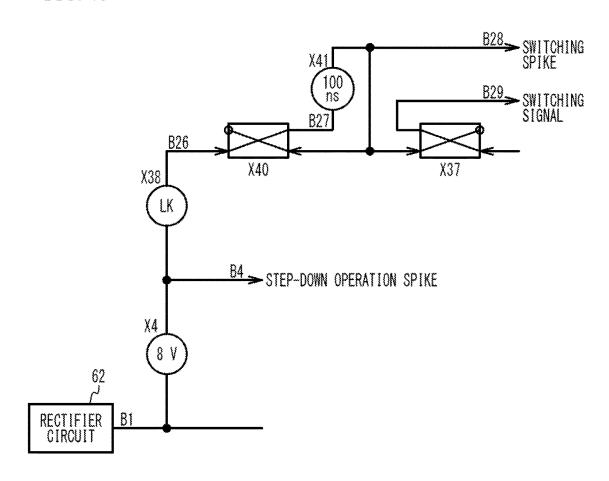

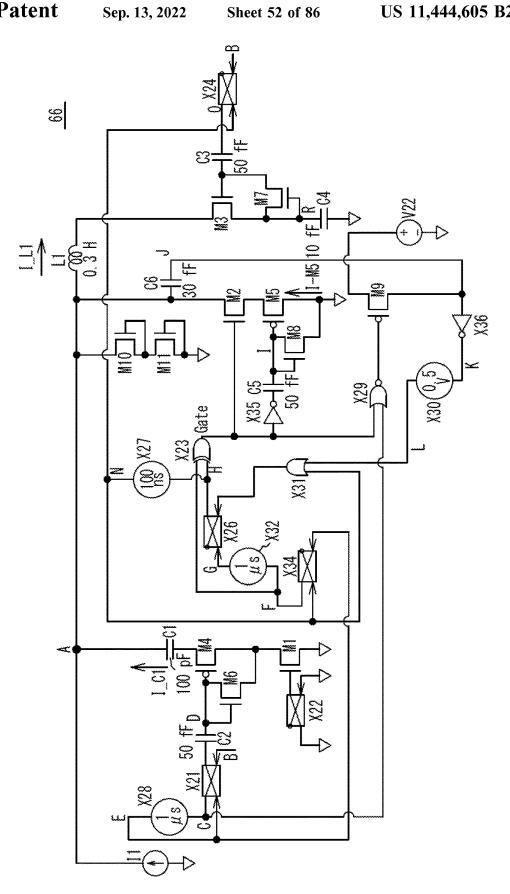

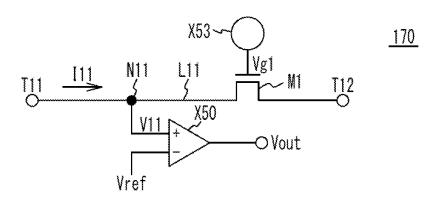

- FIG. 48 is a circuit diagram of the determination circuit in the seventh embodiment;

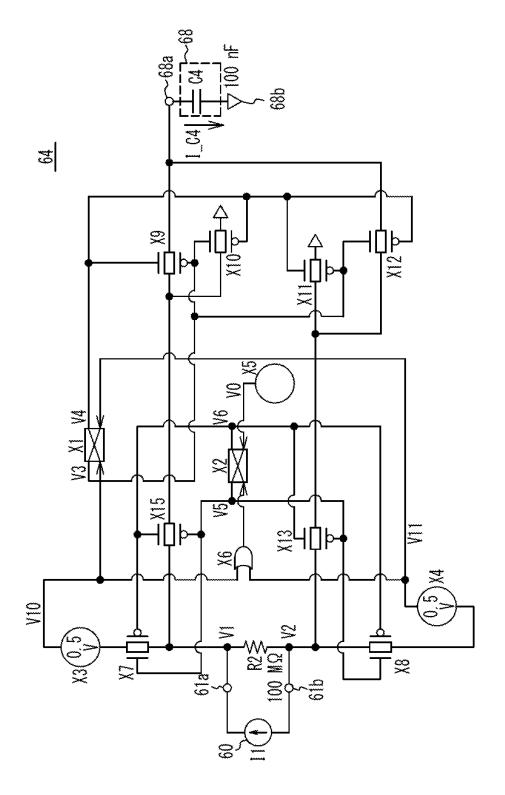

- FIG. 49 illustrates respective voltages of nodes in the determination circuit with respect to time in the seventh embodiment;

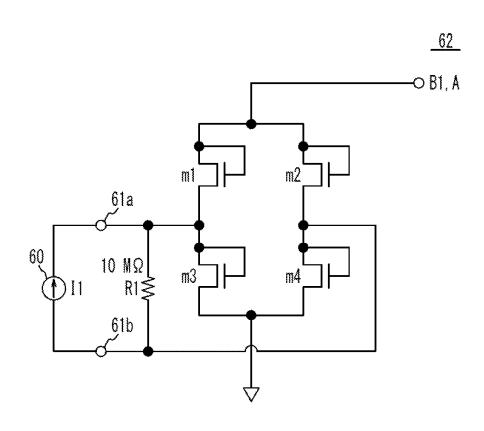

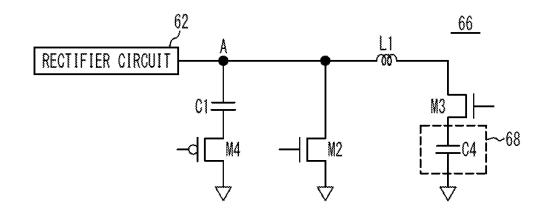

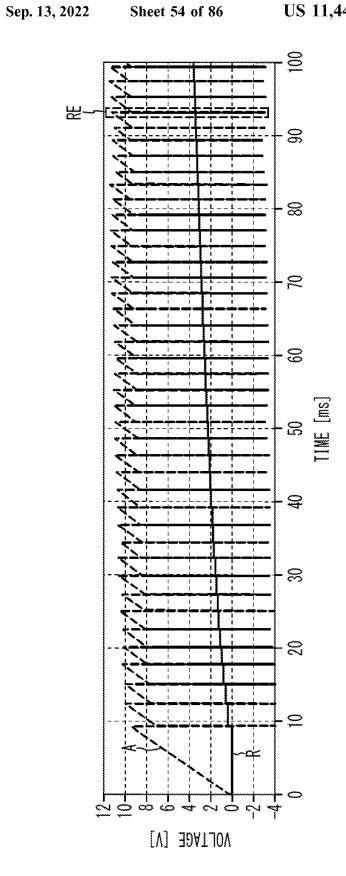

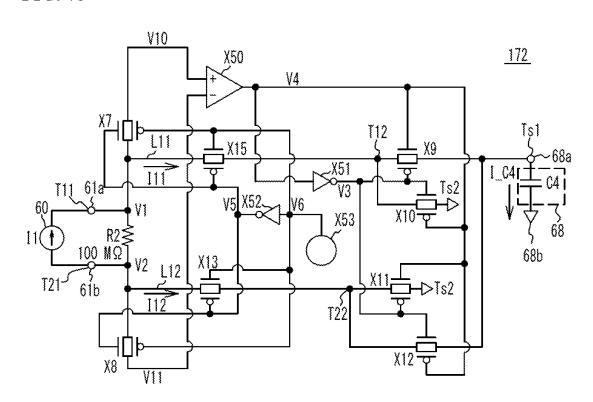

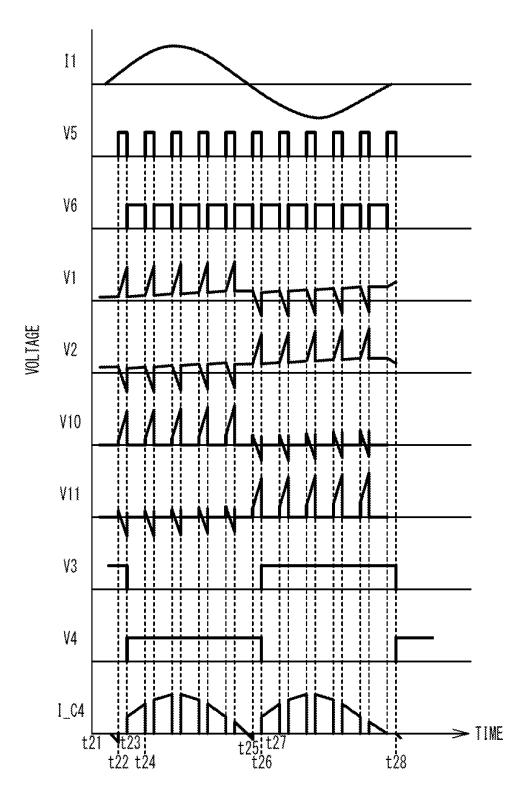

- FIG. 50 is a circuit diagram illustrating a rectifier circuit in the seventh embodiment;

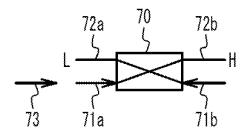

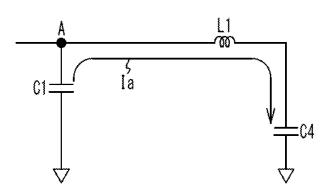

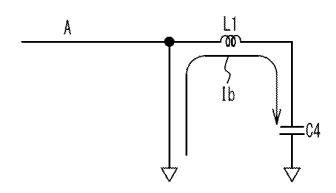

- FIG. **51**A to FIG. **51**C are schematic views of a step-down circuit in the seventh embodiment;

- FIG. **52** is a circuit diagram of the step-down circuit in the seventh embodiment;

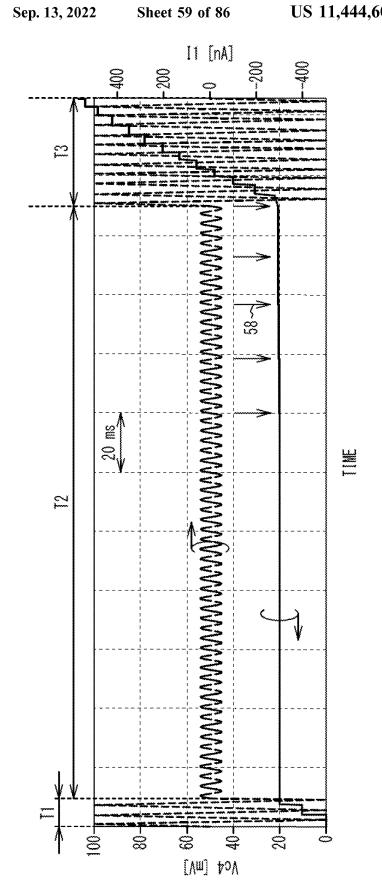

- FIG. 53 illustrates respective voltages of nodes in the step-down circuit with respect to time in the seventh embodiment;

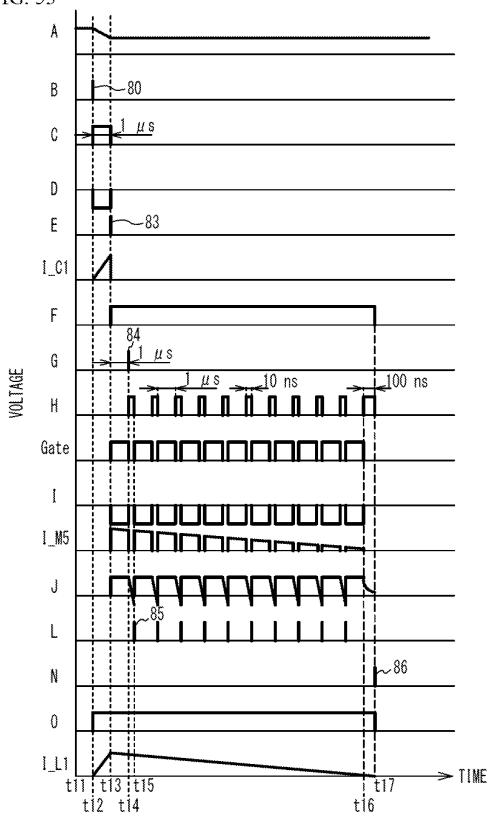

- FIG. **54** illustrates respective voltages of nodes A and R with respect to time in the seventh embodiment;

- FIG. **55**A to FIG. **55**C are schematic views of a synchronous rectifier circuit in the seventh embodiment;

- FIG. **56** is a circuit diagram of the synchronous rectifier circuit in the seventh embodiment;

- FIG. **57** illustrates respective voltages of nodes in the 50 synchronous rectifier circuit with respect to time in the seventh embodiment;

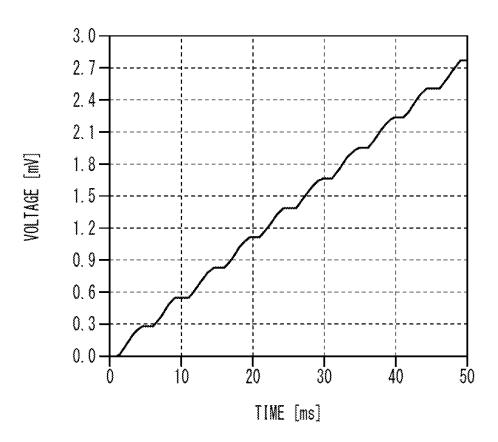

- FIG. **58** illustrates the voltage of a capacitor charged by the synchronous rectifier circuit with respect to time in the seventh embodiment:

- FIG. **59** illustrates a generated current and the voltage of the capacitor with respect to time in the seventh embodiment;

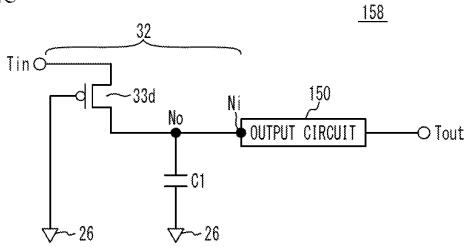

- FIG. **60**A and FIG. **60**B are circuit diagrams of spike generation circuits in accordance with an eighth embodi- 60 ment and a variation 1 thereof, respectively;

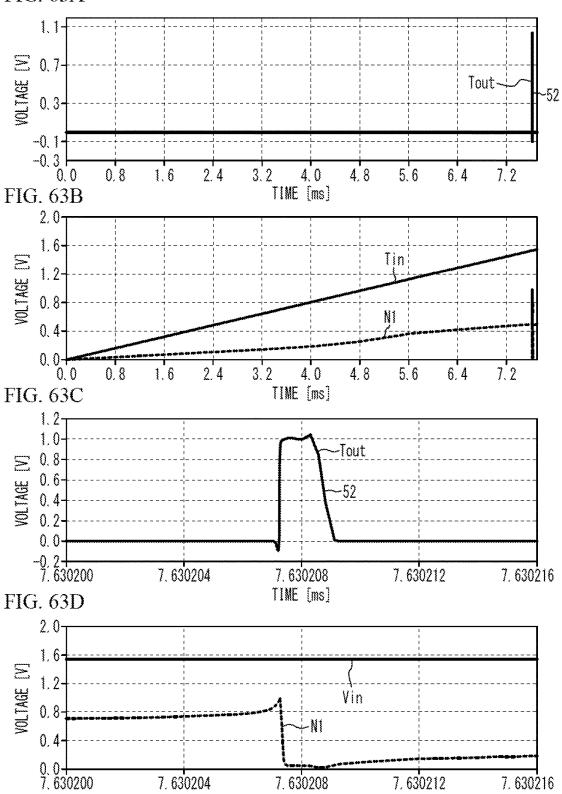

- FIG. **61**A and FIG. **61**B are circuit diagrams of spike generation circuits in accordance with variations 1A and 1 of the eighth embodiment used for a simulation, respectively;

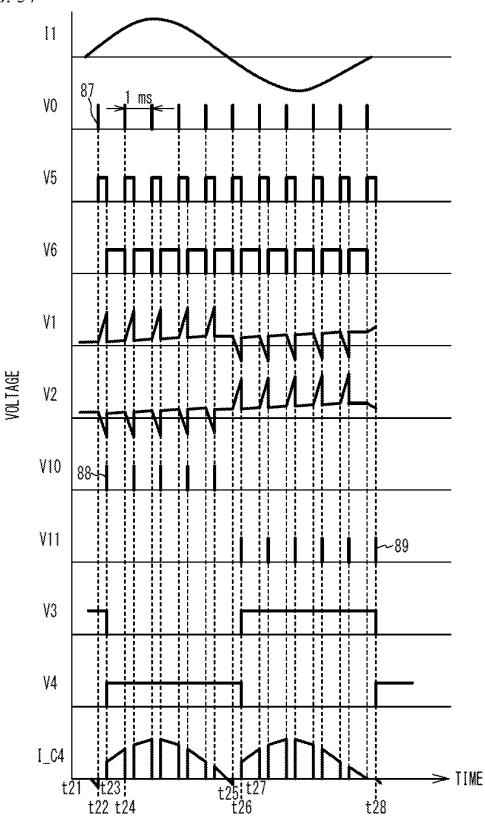

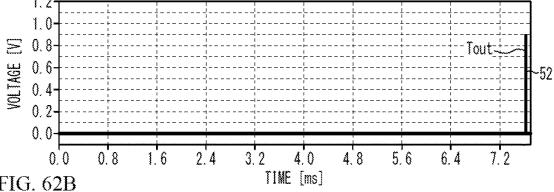

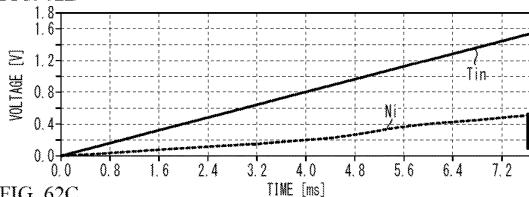

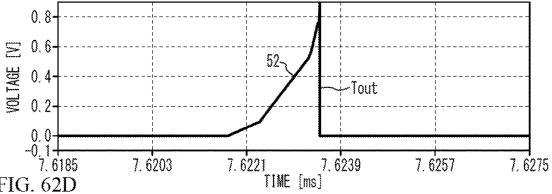

- FIG. **62**A to FIG. **62**D present simulation results of the 65 variation 1A of the eighth embodiment and illustrate voltages with respect to time;

- FIG. 63A to FIG. 63D present simulation results of the variation 1 of the eighth embodiment and illustrate voltages with respect to time;

- FIG. **64**A to FIG. **64**C are circuit diagrams of spike generation circuits in accordance with variations 2 to 4 of the eighth embodiment, respectively;

- FIG. **65** is a circuit diagram of a spike generation circuit in accordance with a variation 5 of the eighth embodiment;

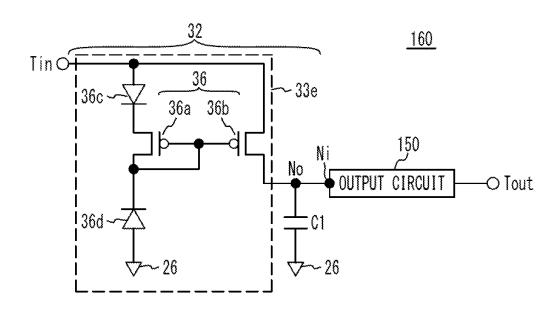

- FIG. **66**A and FIG. **66**B are circuit diagrams of spike generation circuits in accordance with variations 5A and 5 of the eighth embodiment used for a simulation, respectively;

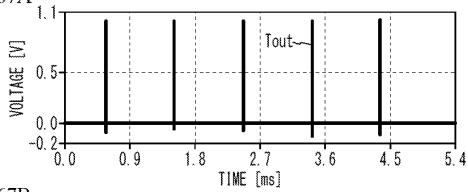

- FIG. 67A and FIG. 67B present simulation results of the variation 5A of the eighth embodiment and illustrate voltage with respect to time, and FIG. 67C and FIG. 67D present simulation results of the variation 5 of the eighth embodiment and illustrate voltages with respect to time;

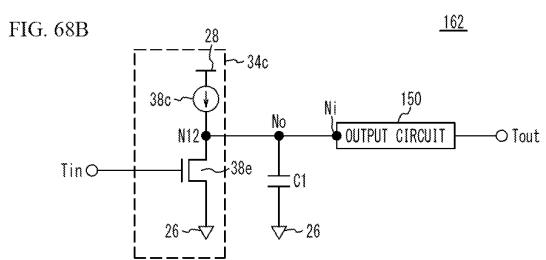

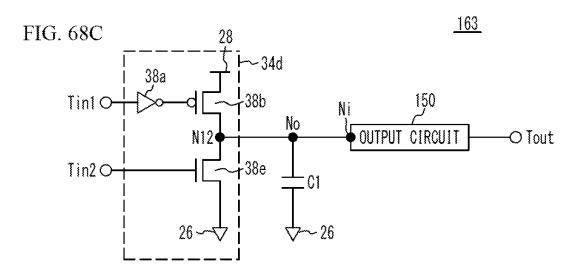

- FIG. **68**A to FIG. **68**C are circuit diagrams of spike generation circuits in accordance with variations 6 to 8 of the eighth embodiment, respectively;

- FIG. **69**A to FIG. **69**C are circuit diagrams of spike generation circuits in accordance with variations 9 to 11 of the eighth embodiment, respectively;

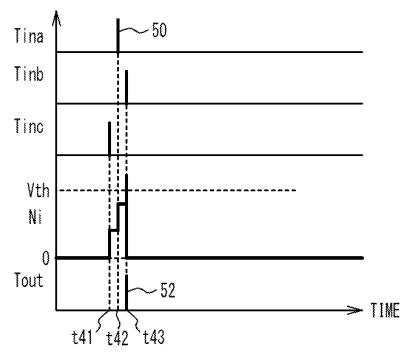

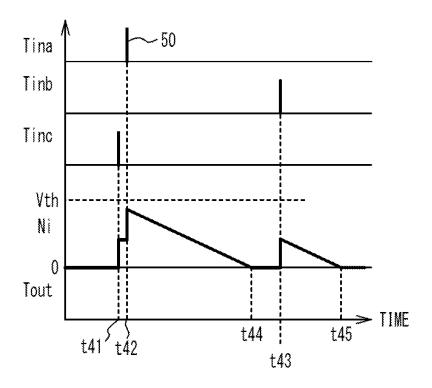

- FIG. **70**A and FIG. **70**B illustrate voltages with respect to time in the variation 9 of the eighth embodiment;

- FIG. 71 is a block diagram of a detector in accordance with a ninth embodiment;

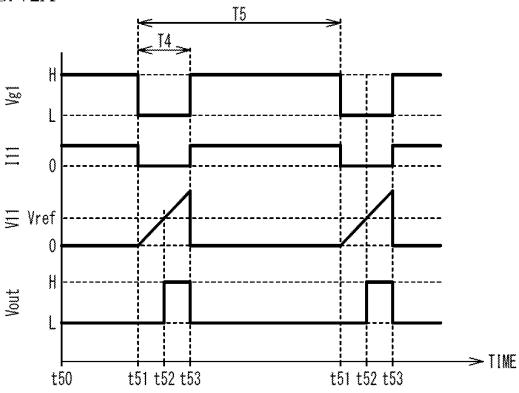

- FIG. 72A and FIG. 72B illustrate voltages in the detector in accordance with the ninth embodiment with respect to time:

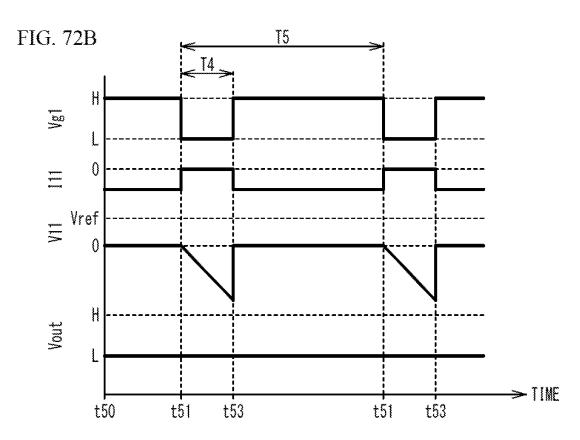

- FIG. **73** is a block diagram of a detector in accordance with a variation 1 of the ninth embodiment;

- FIG. **74** illustrates respective voltages in the detector in accordance with the variation 1 of the ninth embodiment with respect to time:

- FIG. 75 is a circuit diagram of a synchronous rectifier circuit in accordance with a variation 3 of the ninth embodiment:

- FIG. **76** illustrates respective voltages of nodes in the synchronous rectifier circuit in accordance with the variation 3 of the ninth embodiment with respect to time;

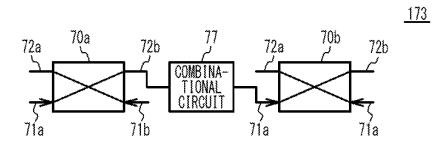

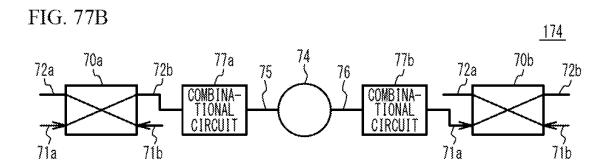

- FIG. 77A and FIG. 77B are block diagrams of electronic circuits in accordance with a first comparative example and a tenth embodiment, respectively;

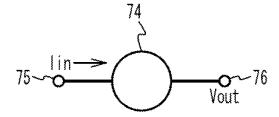

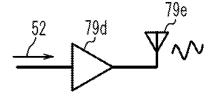

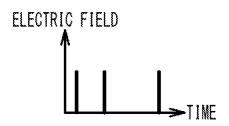

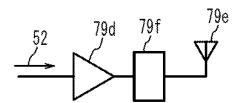

- FIG. **78**A illustrates a spike generation circuit, FIG. **78**B illustrates an internal state S with respect to time, and FIG. **78**C illustrates an output voltage Vout with respect to time;

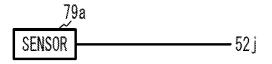

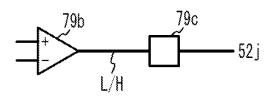

- FIG. **79**A and FIG. **79**B are block diagrams of the electronic circuits in accordance with the first comparative example and the tenth embodiment, respectively;

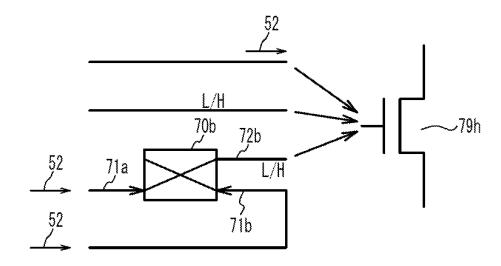

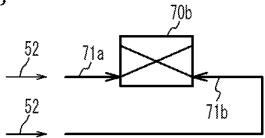

- FIG. **80**A and FIG. **80**B illustrate examples of the electronic circuit in accordance with the tenth embodiment;

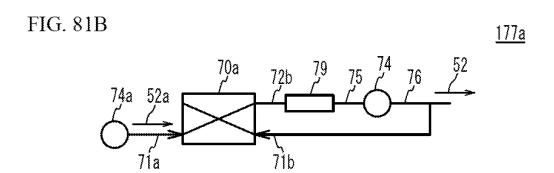

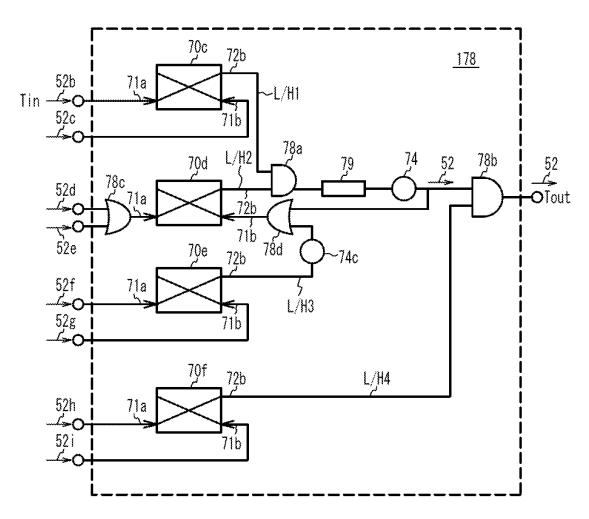

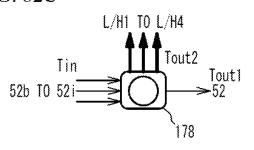

- FIG. **81**A and FIG. **81**B are block diagrams of electronic circuits in accordance with variations 1 and 2 of the tenth embodiment, respectively;

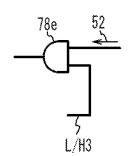

- FIG. **82**A and FIG. **82**B are block diagrams of an electronic circuit in accordance with a variation 3 of the tenth embodiment, and FIG. **82**C illustrates a symbol of the electronic circuit in accordance with the variation 3 of the tenth embodiment;

- FIG. **83**A and FIG. **83**B illustrate exemplary spike signals input to the electronic circuit in the variation 3 of the tenth embodiment;

- FIG. **84**A and FIG. **84**B illustrate exemplary circuits in which the spike signal output from the electronic circuit in the variation 3 of the tenth embodiment is used;

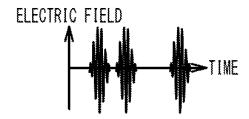

- FIG. **85**A and FIG. **85**C are circuit diagrams illustrating examples where the spike signal output from the electronic

circuit in the variation 3 of the tenth embodiment is used, and FIG. **85**B and FIG. **85**D illustrate the magnitude of an electromagnetic wave output from an antenna; and

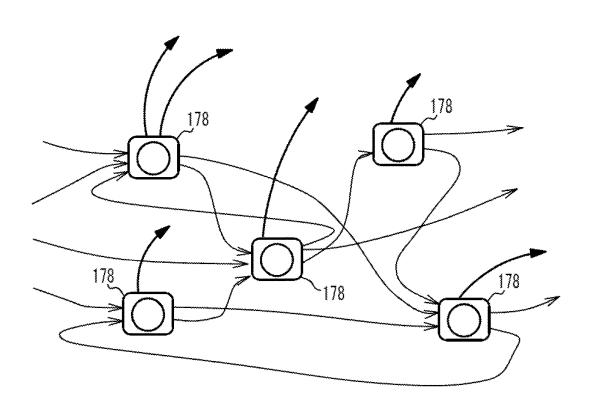

FIG. **86** is a schematic view of a network circuit in accordance with a variation 4 of the tenth embodiment.

## MODES FOR CARRYING OUT THE INVENTION

Spike generator circuits such as neuron circuits are <sup>10</sup> required to reduce their power consumption.

Embodiments of the present disclosure are made in view of above problems, and the objective thereof is to reduce the power consumption.

Hereinafter, with reference to the accompanying drawings, a description will be given of embodiments of the present invention.

### First Embodiment

FIG. 1A and FIG. 1B are circuit diagrams of spike generation circuits in accordance with a first embodiment and a variation 1 thereof, respectively. As illustrated in FIG. 1A, a spike generation circuit 130 of the first embodiment includes an inverter 12, a field effect transistor (FET) 14, an inverting circuit 16, and a delay circuit 17. The inverter 12 is a complementary metal oxide semiconductor (CMOS) inverter, and includes an N-channel FET (NFET) 13a, and a P-channel FET (PFET) 13b.

The source of the NFET 13a is coupled to a ground line 26, the drain is coupled to a node N1, and the gate is coupled to a node NO. The source of the PFET 13b is coupled to a power line 28, the drain is coupled to the node N1, and the gate is coupled to the node NO. The node NO is the input 35 node of the inverter 12, and the node N1 is the output node of the inverter 12. The FET 14 is a PFET, and is connected in series with the PFET 13b between the node N1 and the power line 28 through the PFET 13b, and the drain is 40 coupled to the node N1.

The inverting circuit 16 inverts the level of the node N1, and outputs the inverted level to the gate of the FET 14. The delay circuit 17 delays the level of the node N1, and outputs the delayed level to a node N3. The node N3 is coupled to 45 the input node NO of the inverter 12 and an output terminal Tout. The inverting circuit 16 and the FET 14 form a positive feedback loop 15. An input terminal Tin is coupled to an intermediate node Ni in the positive feedback loop 15. Note that the location of the intermediate node Ni in the positive 50 feedback loop 15 is specifically illustrated in FIG. 2A, FIG. 3A, FIG. 4A, and FIG. 5A.

[Variation 1 of the First Embodiment]

As illustrated in FIG. 1B, in a spike generation circuit 131 of the variation 1 of the first embodiment, the FET 14 is an 55 NFET, and is connected in series with the NFET 13a between the node N1 and the ground line 26. The source of the FET 14 is coupled to the ground line 26 through the NFET 13a, and the drain is coupled to the node N1. Other configurations are the same as those of the first embodiment, 60 and the description thereof is thus omitted.

A description will be given of a variation 2 of the first embodiment where the intermediate node Ni, to which the input terminal Tin is coupled, in the first embodiment is the node N1, and a variation 3 of the first embodiment where the 65 intermediate node Ni in the first embodiment is provided in the inverting circuit 16.

10

[Variation 2 of the First Embodiment]

The variation 2 of the first embodiment is an example where the intermediate node Ni in the first embodiment is the node N1. FIG. 2A is a circuit diagram of a spike generation circuit in accordance with the variation 2 of the first embodiment, and FIG. 2B illustrates respective voltages of the node N1 and the output terminal Tout. As illustrated in FIG. 2A, in a spike generation circuit 132, the input terminal Tin is coupled to the nodes N1 and Ni. Therefore, the input signal is input to the node N1. Other configurations are the same as those of the first embodiment, and the description thereof is thus omitted.

Although the order of the description of the circuit operation is back and forth, the circuit operation of the variation 2 of the first embodiment will be described first using FIG. 2B. The case illustrated in FIG. 2B is a case where the voltage of the node N1 increases from 0 V at a constant rate, and the description will be given of this operation. This case corresponds to a case where a constant current is applied to the input terminal Tin. At time to, the voltage of the node N1 is a low level (0 V). The output of the inverting circuit 16 is a high level, and the FET 14 is off. The voltage of the output terminal Tout is the low level (0 V). Since the FET 14 is off, the inverter 12 does not function.

The voltage of the node N1 increases at a constant rate with time. When the voltage of the node N1 is lower than the threshold voltage Vth of the inverting circuit 16, the output of the inverting circuit 16 is the high level, the output of the delay circuit 17 is the low level, and the voltage of the output terminal Tout maintains the low level. As described above, the threshold voltage Vth is set for the inverting circuit 16.

When the voltage of the node N1 reaches the threshold voltage Vth of the inverting circuit 16 at time t1, the inverting circuit 16 outputs the low level. The FET 14 is turned on, and thereby, the inverter 12 is activated. The input node of the inverter 12 is NO, and the output node of the inverter 12 is N1. When the FET 14 is off, the FET 13b and the node N1 are disconnected, and thereby the inverter 12 does not function as the inverter. When the FET 14 is turned on, the FET 13b and the node N1 are connected, and the function as the inverter is obtained. "The function as the inverter is obtained." Since the voltage of the output terminal Tout is the low level, the inverter 12 changes the voltage of the node N1 to the high level (Vdd).

At time t2 delayed from time t1 by the delay time  $\Delta T$  of the delay circuit 17, the output of the delay circuit 17 becomes the high level. The FET 13a changes from off to on. The inverter 12 changes the node N1 to the low level. The output of the inverting circuit 16 becomes the high level, and the FET 14 is turned off. The voltage of the node N1 returns to the low level. At time t3 delayed from time t2 by  $\Delta T$ , the delay circuit 17 changes the voltage of the output terminal Tout to the low level. This causes a spike signal 52 having a pulse width equal to the delay time of the delay circuit 17 to be output from the output terminal Tout. As described above, since the spike signal having a pulse width corresponding to the delay time of the delay circuit 17 has a narrow pulse width, the power consumption can be reduced.

[Variation 3 of the First Embodiment]

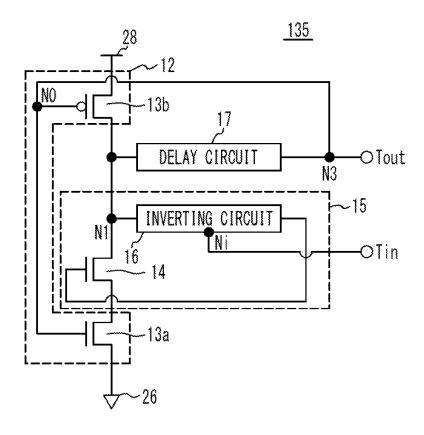

The variation 3 of the first embodiment is an example where the intermediate node Ni in the first embodiment is provided in the inverting circuit 16. Examples of the location where the intermediate node Ni is provided will be described in a fourth embodiment and variations thereof. FIG. 3A is a circuit diagram of a spike generation circuit in accordance with the variation 3 of the first embodiment, and FIG. 3B illustrates respective voltages of the nodes Ni and N1 and the

output terminal Tout. As illustrated in FIG. 3A, in a spike generation circuit 133, the input terminal Tin is coupled to the intermediate node Ni provided in the inverting circuit 16. Other configurations are the same as those of the first embodiment, and the description thereof is thus omitted.

As illustrated in FIG. 3B, at time to, the voltage of the node Ni is the low level, and the gate of the FET 14 is at the high level. At time t0, the FET 13a is in an on-state. The FET 14 is off, and the voltage of the node N1 is the low level. The voltage of the output terminal Tout is the low level. The voltage of the node Ni increases at a constant rate with time. When the voltage of the node Ni reaches the threshold voltage Vth at time t1, the gate of the FET 14 becomes at the low level. Since the FET 14 is turned on and the inverter 12 thereby functions, the node N1 becomes at the high level. When the voltage of the output terminal Tout becomes the high level at time t2 delayed from time t1 by the delay time  $\Delta T$  of the delay circuit 17, the node N1 is changed to the low level by the inverter 12. At time t3, the output terminal Tout 20 becomes at the low level. The operations thereafter are the same as those of the variation 2 of the first embodiment, and the description thereof is thus omitted.

A description will be given of a variation 4 of the first embodiment where the intermediate node Ni, to which the 25 input terminal Tin is coupled, in the variation 1 of the first embodiment is the node N1, and a variation 5 of the first embodiment where the intermediate node Ni in the variation 1 of the first embodiment is provided in the inverting circuit

[Variation 4 of the First Embodiment]

The variation 4 of the first embodiment is an example where the intermediate node Ni in the variation 1 of the first embodiment is the node N1. FIG. 4A is a circuit diagram of a spike generation circuit in accordance with the variation 4 of the first embodiment, and FIG. 4B illustrates respective voltages of the node N1 and the output terminal Tout. As illustrated in FIG. 4A, in a spike generation circuit 134, the input terminal Tin is coupled to the nodes N1 and Ni. Therefore, the input signal is input to the node N1. Other configurations are the same as those of the variation 1 of the first embodiment, and the description thereof is thus omitted.

A case where the voltage of the node N1 decreases from Vdd at a constant rate as illustrated in FIG. 4B will be described. This case corresponds to a case where a constant 45 current is applied to the input terminal Tin when a capacitor is shunt-connected between the input terminal Tin and the intermediate node Ni as illustrated in FIG. 19B of a variation 3 of the third embodiment described later. At time to, the voltage of the node N1 is the high level (Vdd). The output of the inverting circuit 16 is the low level (0 V), and the FET 14 is off. The voltage of the output terminal Tout is the high level. Since the FET 14 is off, the inverter 12 does not function

The voltage of the node N1 decreases at a constant rate 55 with time. When the voltage of the node N1 is higher than the threshold voltage Vth of the inverting circuit 16, the output of the inverting circuit 16 is the low level, the output of the delay circuit 17 is the high level, and the voltage of the output terminal Tout maintains the high level.

When the voltage of the node N1 reaches the threshold voltage Vth of the inverting circuit 16 at time t1, the inverting circuit 16 outputs the high level. The FET 14 is turned on, and thereby, the inverter 12 is activated. Since the voltage of the output terminal Tout is the high level, the 65 inverter 12 changes the voltage of the node N1 to the low level (0 V).

12

At time t2, the output of the delay circuit 17 becomes the low level. The inverter 12 changes the node N1 to the high level. The output of the inverting circuit 16 becomes the low level, and the FET 14 is turned off. The voltage of the node N1 returns to the high level. At time t3, the delay circuit 17 changes the voltage of the output terminal Tout to the high level. This causes the spike signal 52 with a width of  $\Delta T$  to be output from the output terminal Tout.

[Variation 5 of the First Embodiment]

The variation 5 of the first embodiment is an example where the intermediate node Ni in the variation 1 of the first embodiment is provided in the inverting circuit 16. Examples of the location where the intermediate node Ni is provided will be described in the fourth embodiment and the variations thereof. FIG. 5A is a circuit diagram of a spike generation circuit in accordance with the variation 5 of the first embodiment, and FIG. 5B illustrates respective voltages of the nodes Ni and N1 and the output terminal Tout. As illustrated in FIG. 5A, in a spike generation circuit 135, the input terminal Tin is coupled to the inside of the inverting circuit 16. Other configurations are the same as those of the variation 1 of the first embodiment, and the description thereof is thus omitted.

As illustrated in FIG. **5**B, when the voltage of the node Ni reaches the threshold voltage Vth at time **11**, the inverting circuit **16** outputs the high level. The FET **14** is turned on, and the node N**1** becomes at the low level. The operations thereafter are the same as those of the variation **4** of the first embodiment, and the description thereof is thus omitted.

In the first embodiment and the variations thereof, the inverter 12 (a first CMOS inverter) is connected between the ground line 26 and the power line 28 (between a first power supply and a second power supply), and the output node of the inverter 12 is coupled to the node N1 (a first node). The FET 14 (a switch or a first switch) is connected in series with the inverter 12 between the ground line 26 and the power line 28. The inverting circuit 16 (a first inverting circuit) outputs an inversion signal of the signal of the node N1 to the gate (a control terminal) of the FET 14. The delay circuit 17 delays the signal of the node N1 and outputs the delayed signal to the input node of the inverter 12, and outputs the output spike signal 52 to the output terminal Tout.

In such a configuration, the node N1 is the intermediate node Ni coupled to the input terminal Tin to which the input signal is input, in the variations 2 and 4 of the first embodiment. Therefore, as illustrated in FIG. 2B and FIG. 4B, when the voltage of the node N1 exceeds the threshold voltage Vth at time t1, the inverting circuit 16 changes the gate of the FET 14 to the high level (FIG. 2B) or the low level (FIG. 4B). This causes the FET 14 to be turned on, causing the node N1 to be at the high level (FIG. 2B) or at the low level (FIG. 4B). In this manner, positive feedback is applied through the inverting circuit 16.

When the delay circuit 17 outputs the high level (FIG. 2B) or the low level (FIG. 4B) at time t2, the output of the inverter 12 inverts, and the node N1 becomes at the low level (FIG. 2B) or at the high level (FIG. 4B). In this manner, negative feedback is applied through the delay circuit 17.

Therefore, the rise and fall of the spike signal 52 steepen, and the spike signal 52 with a narrow pulse width can be generated. Since the FET 13a or 13b is turned off, the current penetrating from the power line 28 to the ground line 26 is reduced. In addition, since the FET 14 is turned off, the current penetrating to the ground line 26 from the power line 28 can be reduced. This can reduce the power consumption. In the first embodiment and the variations thereof, the

inverting circuit 16 and the delay circuit 17 may share each other's components in part or in whole.

In the variations 3 and 5 of the first embodiment, the intermediate node Ni coupled to the input terminal Tin is provided in the inverting circuit 16. This configuration 5 applies positive feedback from the node N1 through the inverting circuit 16 at time t1 as illustrated in FIG. 3B and FIG. 5B. Negative feedback is applied from the node N1 through the delay circuit 17 at time t2. Therefore, the spike signal 52 with a narrow pulse width can be generated, and 10 the power consumption can be reduced.

#### Second Embodiment

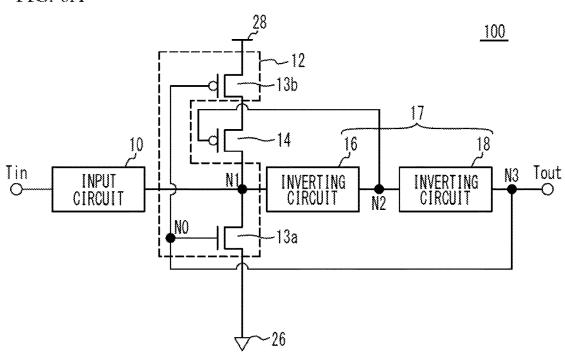

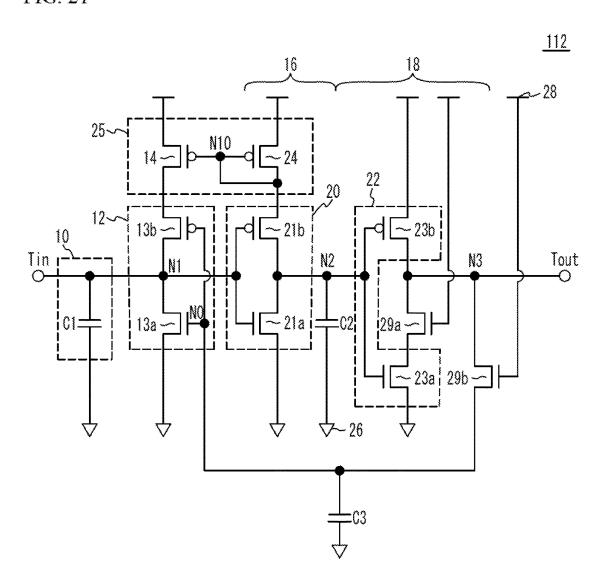

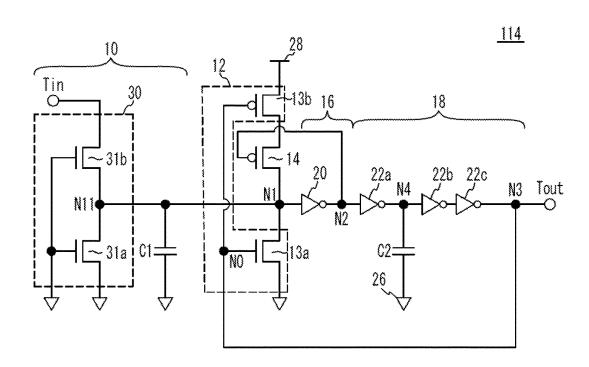

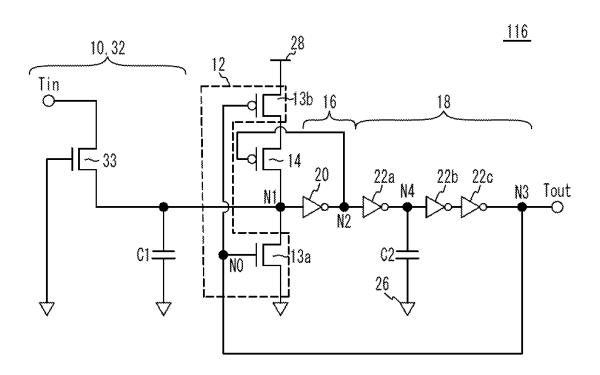

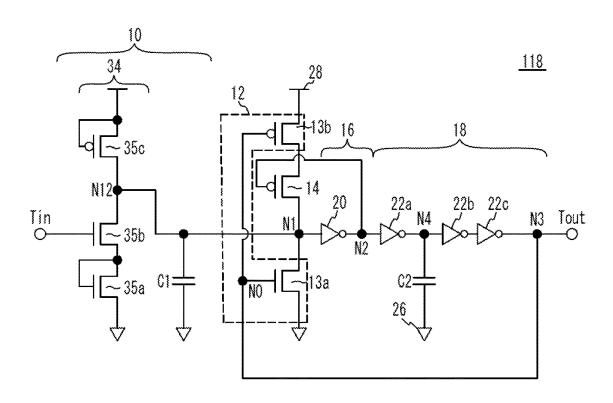

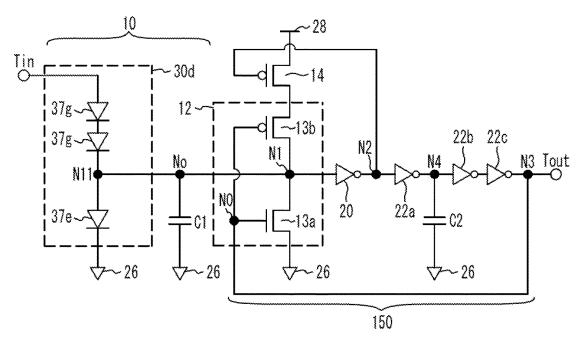

A second embodiment is a specific example of the variations 2 and 4 of the first embodiment, and an exemplary spike generation circuit used in neuron circuits and the like. FIG. 6A is a circuit diagram of a spike generation circuit in accordance with the second embodiment, and FIG. 6B illustrates voltages with respect to time. As illustrated in 20 FIG. 6A, a spike generation circuit 100 of the second embodiment includes an input circuit 10, the inverter 12, the FET 14, and inverting circuits 16 and 18. The inverting circuits 16 and 18 form the delay circuit 17. The input circuit 10 is a circuit that sets conditions for generating a spike 25 signal with respect to the input signal input to the input terminal Tin. The inverter 12 is a CMOS inverter, and includes the NFET 13a and the PFET 13b.

The source of the NFET 13a is coupled to the ground line 26, the drain is coupled to the node N1, and the gate is 30 coupled to the node NO. The source of the PFET 13b is coupled to the power line 28, the drain is coupled to the node N1, and the gate is coupled to the node NO. The nodes NO and N1 are the input node and the output node of the inverter 12, respectively. The FET 14 is a PFET, and is connected in 35 series with the PFET 13b between the node N1 and the power line 28. The source of the FET 14 is coupled to the power line 28 through the PFET 13b, and the drain is coupled to the node N1.

The inverting circuit 16 inverts the level of the node N1, 40 and outputs the inverted level to the gate of the FET 14 and a node N2. The inverting circuit 18 inverts the level of the node N2, and outputs the inverted level to the node N3. The node N3 is coupled to the input node NO of the inverter 12 and the output terminal Tout.

FIG. 6B illustrates respective voltages of the input terminal Tin, the node N1, and the output terminal Tout with respect to time. An integrating circuit that integrates the input signal that has been input to the input terminal Tin and outputs the resulting signal to the node N1 will be described 50 as an example of the input circuit 10.

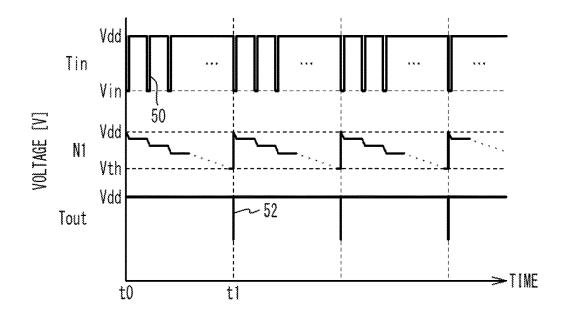

The respective voltages of the input terminal Tin and the output terminal Tout during a steady state are equal to the voltage (0 V) of the ground line 26. Immediately before time to, the voltage of the node N1 is 0 V. The node N2 is at the high level, and the node N3 is at the low level. The gate of the FET 14 is at the high level, and the FET 14 is off. Since the input node of the inverter 12 is at the low level and the FET 14 is off, the node N1 is disconnected from the ground line 26 and the power line 28. Therefore, immediately before 60 time t0, the voltage of the node N1 is maintained.

During the time period between time t0 and time t1, a spike signal 50 is input to the input terminal Tin as the input signal in time series. When the spike signal 50 is input to the input terminal Tin, the voltage of the input terminal Tin 65 becomes Vin higher than 0 V. The input circuit 10 increases the voltage of the node N1 each time the spike signal 50 is

14

input. This gradually increases the voltage of the node N1. When the voltage of the node N1 is lower than the threshold voltage Vth of the inverting circuit 16, the node N2 is at the high level, and the node N3 is at the low level. Therefore, the voltage of the output terminal Tout is maintained at  $0 \, V$ . The node N1 is disconnected from the ground line 26 and the power line 28.

At time t1, the voltage of the node N1 exceeds the threshold voltage Vth. The inverting circuit 16 changes the node N2 from the high level to the low level. Since the low level is applied to the gate of the FET 14, the FET 14 is turned on, and positive feedback is applied to the node N1. This causes the node N1 to rise to the high level (the voltage Vdd of the power line 28). When the node N2 changes from the high level to the low level, the inverting circuit 18 changes the node N3 from the low level to the high level. Since the input node NO of the inverter 12 becomes at the high level, negative feedback is applied to the node N1, and the node N1 falls to the low level (the voltage 0 V of the ground line). The node N2 becomes at the high level and the node N3 becomes at the low level, and the spike signal 52 with a narrow pulse width is output to the output terminal Tout. The FET 14 is turned off, and the node N1 is disconnected from the ground line 26 and the power line 28.

Since the spike signals **50** are successively input as the input signal to the input terminal Tin in time series, after time **11**, in the same manner, every time the voltage of the node N1 exceeds the threshold voltage Vth, the spike signal **52** is output to the output terminal Tout. As seen above, since negative feedback is applied to the node N1 immediately after positive feedback is applied to the node N1, the spike signal **52** with a narrow pulse width can be generated. In addition, immediately after the FET **13** is turned on by the positive feedback, the FET **13** is turned on by the negative feedback simultaneously. Therefore, a current penetrating to the ground line **26** from the power line **28** can be reduced. Thereby, the power consumption can be reduced.

[Variation 1 of the Second Embodiment]

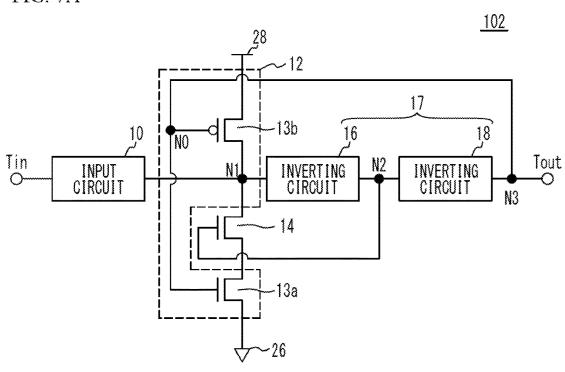

FIG. 7A is a circuit diagram of a spike generation circuit in accordance with a variation 1 of the second embodiment, and FIG. 7B illustrates voltages with respect to time. In a spike generation circuit 102 of the variation 1 of the second embodiment, the FET 14 is an NFET, and is connected in series with the NFET 13a between the node N1 and the ground line 26. The source of the FET 14 is coupled to the ground line 26 through the NFET 13a, and the drain is coupled to the node N1. The node N2 is coupled to the gate of the FET 14. Other configurations are the same as those of the second embodiment illustrated in FIG. 6A, and the description thereof is thus omitted.

FIG. 7B illustrates respective voltages of the input terminal Tin, the node N1, and the output terminal Tout. The voltages of the input terminal Tin and the output terminal Tout during a steady state are equal to the voltage Vdd of the power line 28. Immediately before time to, the voltage of the node N1 is Vdd.

During the time period between time t0 and time t1, the spike signal 50 is input to the input terminal Tin in time series. When the spike signal 50 is input, the voltage of the input terminal Tin becomes Vin lower than Vdd. The input circuit 10 integrates the spike signal 50, and outputs the resulting signal to the node N1. This gradually decreases the voltage of the node N1 when the voltage of the node N1 is higher than the threshold voltage Vth of the inverting circuit 16, the node N2 is at the low level, and the node N3 is at the high level. Therefore, the voltage of the output terminal Tout

is maintained at Vdd. In the variation 1 of the second embodiment, the case where the voltage decreases corresponds to the rise, and the case where the voltage increases corresponds to the fall.

At time t1, the voltage of the node N1 becomes lower than 5 the threshold voltage Vth. The inverting circuit 16 changes the node N2 from the low level to the high level. Since the high level is applied to the gate of the FET 14, the FET 14 is turned on, and positive feedback is applied to the node N1. This causes the node N1 to rise to the low level. When the 10 node N2 changes from the low level to the high level, the inverting circuit 18 changes the node N3 from the high level to the low level. Since the input node NO of the inverter 12 becomes at the low level, negative feedback is applied to the node N1, and the node N1 falls to the high level. This causes 15 the spike signal 52 with a narrow pulse width to be output to the output terminal Tout.

As seen above, the variation 1 of the second embodiment can generate the spike signal 52 with a narrow pulse width by adopting an NFET as the FET 14 and providing the FET 20 14 between the ground line 26 and the node N1. In addition, the power consumption can be reduced by the FET 13b.

In FIG. 6B and FIG. 7B, the spike signal 50 is described as an example of the input signal, but the input signal may have an arbitrary waveform. The input circuit 10 may be any 25 circuit that converts the input signal so that the voltage of the node N1 reaches the threshold voltage Vth when the condition for generating the spike signal 52 is satisfied.

In the second embodiment and the variations thereof, the input signal is input to the input terminal Tin. The output 30 node of the inverter 12 (a first CMOS inverter) is coupled to the node N1 (a first node) coupled to the input terminal Tin, and the inverter 12 is connected between the ground line 26 (a first power supply) and the power line 28 (a second power supply having a higher voltage than the first power supply). 35 The FET 14 (a switch) is connected in series with the inverter 12 between the ground line 26 and the power line 28. The inverting circuit 16 (a first inverting circuit) outputs an inversion signal of the signal of the node N1 to the gate (a control terminal) of the FET 14. The delay circuit 17 40 delays the signal of the node N1, and outputs the delayed signal to the input node NO of the inverter 12 and outputs the spike signal 52 (an output spike signal) to the output terminal Tout.

cuit 16 and negative feedback through the delay circuit 17 to be applied, therefore allowing the spike signal 52 with a narrow pulse width to be generated. In addition, since the FET 13b is turned off, the current penetrating to the ground line 26 from the power line 28 can be reduced. Therefore, the 50 power consumption can be reduced.

As described previously, the inverting circuit 16 outputs an inversion signal of the signal of the node N1 to the gate of the FET 14 and the node N2 (a second node). The delay circuit 17 includes the inverting circuit 16, and the inverting 55 circuit 18 that outputs an inversion signal of the signal of the node N2 to the input node NO of the inverter 12 and the node N3 (a third node). This allows the inverting circuit 16 to provide positive feedback of the signal of the node N1 to the gate of the FET 14, and the inverting circuit 18 to provide 60 Capacitor C2: negative feedback of the signal of the node N1 to the input node NO of the inverter 12.

As illustrated in FIG. 6A, when the FET 14 is a PFET (a P-channel transistor), the FET 14 is connected between the node N1 and the power line 28. This configuration allows the 65 positive-going spike signal 52 to be generated as illustrated in FIG. 6B. As illustrated in FIG. 7A, when the FET 14 is

16

an NFET (an N-channel transistor), the FET 14 is connected between the node N1 and the ground line 26. This configuration allows the negative-going spike signal 52 to be generated as illustrated in FIG. 7B.

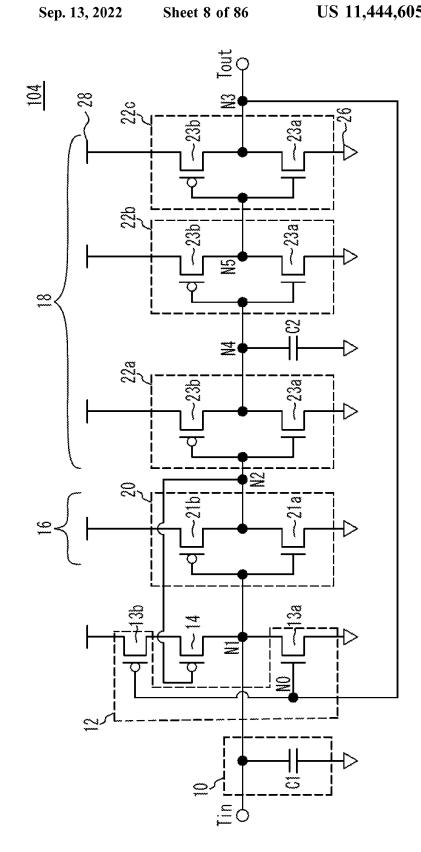

### Third Embodiment

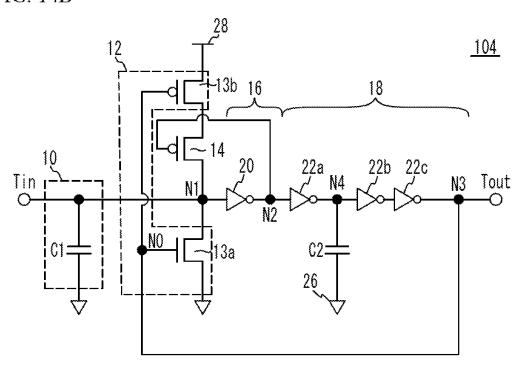

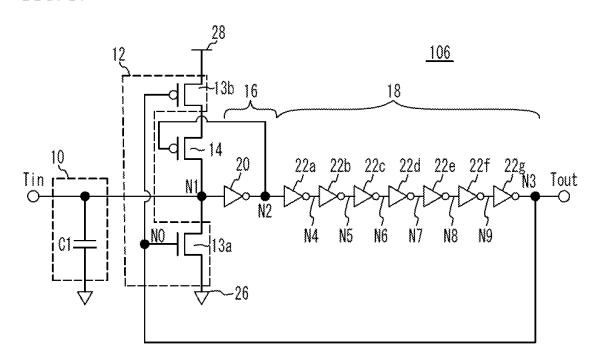

A third embodiment is a specific example of the spike generation circuit in accordance with the second embodiment and the variations thereof. FIG. 8 is a circuit diagram of a spike generation circuit in accordance with the third embodiment. As illustrated in FIG. 8, in a spike generation circuit 104 of the third embodiment, the input circuit 10 is a capacitor C1 having a first end coupled to the node N1 and a second end coupled to the ground line 26.

The inverting circuit 16 is an inverter 20 having an input node coupled to the N1 and an output node coupled to the node N2. The inverter 20 is a CMOS inverter, and includes an NFET 21a and a PFET 21b. The source of the NFET 21a is coupled to the ground line 26, the drain is coupled to the node N2, and the gate is coupled to the node N1. The source of the PFET 21b is coupled to the power line 28, the drain is coupled to the node N2, and the gate is coupled to the node N1.

The inverting circuit 18 includes inverters 22a to 22c and a capacitor C2. The inverters 22a to 22c are connected in multiple stages between the nodes N2 and N3. That is, the inverters 22a to 22c are connected in series with each other between the nodes N2 and N3. The inverters 22a to 22c are CMOS inverters, and each of the inverters 22a to 22c includes an NFET 23a and a PFET 23b. The source of the NFET 23a is coupled to the ground line 26, the drain is coupled to the output node, and the gate is coupled to the input node. The source of the PFET 23b is coupled to the power line 28, the drain is coupled to the output node, and the gate is coupled to the input node. The input node of the inverter 22a is coupled to the node N2, and the output node is coupled to a node N4. The input node of the inverter 22b is coupled to the node N4, and the output node is coupled to a node N5. The input node of the inverter 22c is coupled to the node N5, and the output node is coupled to the node N3. The capacitor C2 has a first end coupled to the node N4, and a second end coupled to the ground line 26. Other configurations are the same as those of the second embodiment, and the description thereof is thus omitted.

Voltages in the third embodiment were simulated using This causes positive feedback through the inverting cir- 45 simulation program with integrated circuit emphasis (SPICE). The simulation conditions are as follows. NFET:

Type: N-channel MOS using silicon on insulator (SOI),

Gate length: 100 nm, Gate width: 100 nm, Threshold voltage: +0.8 V,

Gate capacitance: 1 fF

Type: P-channel MOSFET using SOI,

Gate length: 100 nm, Gate width: 200 nm, Threshold voltage: -0.8 V, Gate capacitance: 1 fF

Capacitor C1:

Capacitance value: 10 fF

Capacitance value: 4 fF

Ground line 26:

Voltage: 0 V

Power line 28:

Voltage Vdd: 1 V

A constant current of 1 pA was applied to the input terminal Tin.

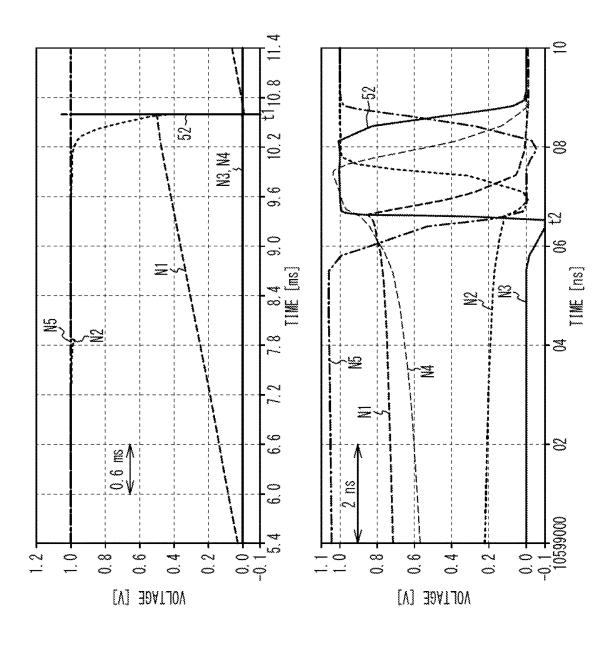

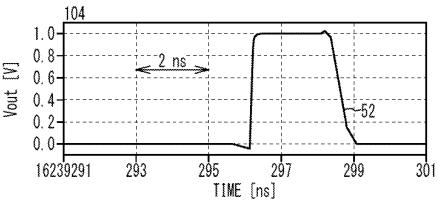

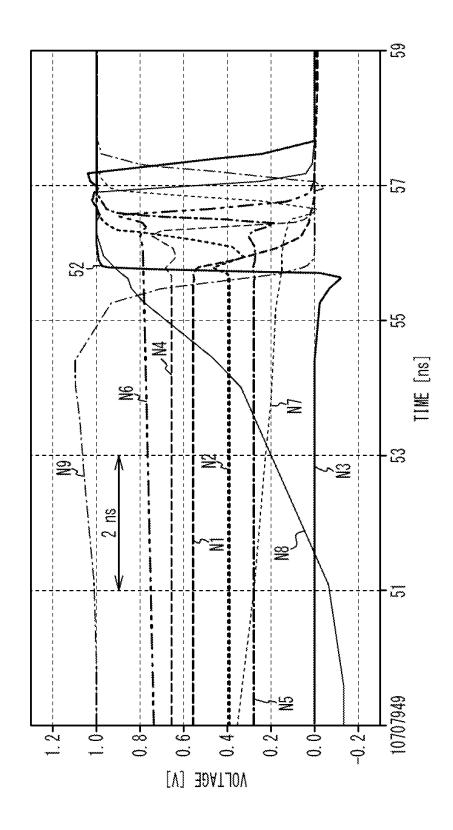

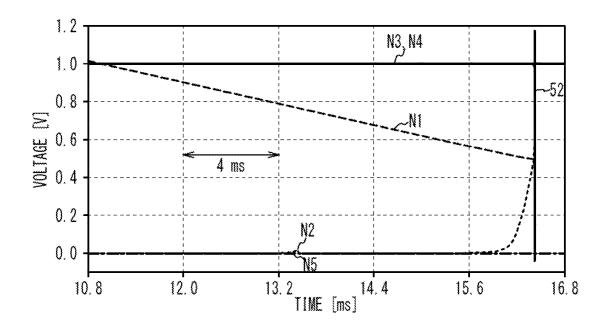

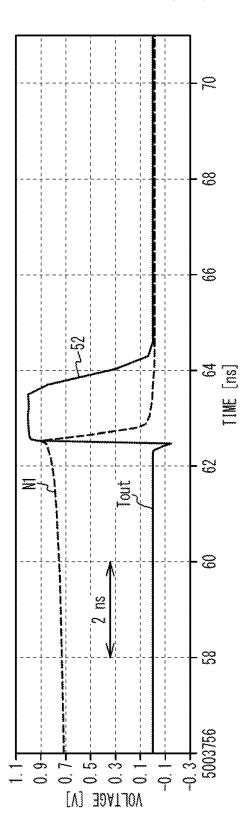

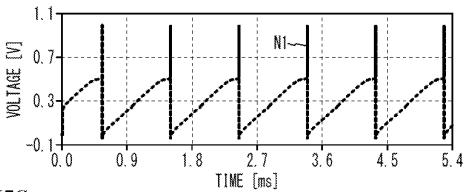

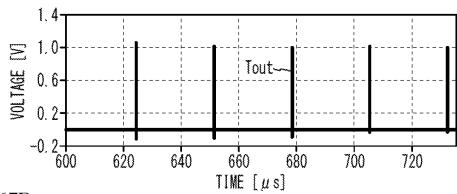

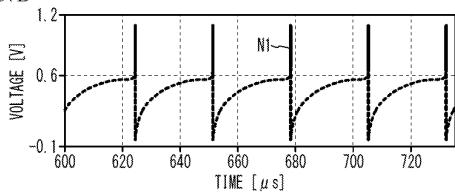

FIG. 9A and FIG. 9B illustrate respective voltages of nodes with respect to time in the third embodiment. FIG. 9B is an enlarged view around the spike signal 52 in FIG. 9A. In FIG. 9B, the first scale of the horizontal axis indicates 10599000 ns corresponding to the time in FIG. 9A, and the subsequent scales indicate only the last two digits. The same applies to enlarged views hereinafter.

As illustrated in FIG. 9A, the voltage of the node N1 increases with time, and when the voltage of the node N1 exceeds 0.5 V, which is the threshold voltage, at time t1, the spike signal 52 is output to the node N3.

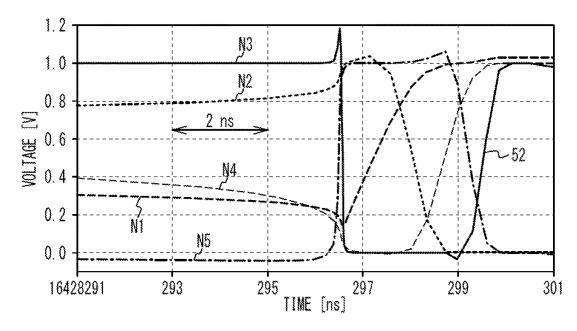

As illustrated in FIG. 9B, during the time period from time t1 to time t2, the voltage of the node N1 increases from 0.5 V to 0.8 V. The voltage of the node N1 rapidly increases in the time axis of FIG. 9A, but gradually increases in the time axis of FIG. 9B. In FIG. 9B, time t1 corresponds to the time prior to the time 10599000 ns. During the time period from time t1 to time t2, the voltage of the node N2 gradually varies from the high level to the low level. The voltage of the node N4 varies from the low level to the high level slightly faster than that of the node N2 during the time period from time t1 to time t2. The voltage of the node N5 varies from the high level to the low level very quickly compared with that of the node N4. The voltage of the node N3 varies from 25 the low level to the high level very steeply at time t2.

At and after time t2, the voltage varies more steeply in the order of the nodes N1, N2, N4, N5, and N3. Therefore, the width of the spike signal 52 is narrow and approximately 2 ns. In addition, the rise and fall of the spike signal 52 steepen. In the CMOS inverter, through-current flows from the power line 28 to the ground line 26 during the transition period of the voltage, but by reducing the leakage current of the NFET and the PFET in the CMOS inverter, the through-current can be sufficiently reduced, and the power consumption can be reduced. Since the rise and fall of the spike signal 52 are steep as described in the third embodiment, the power consumption of the spike generation circuit 104 can be further reduced.

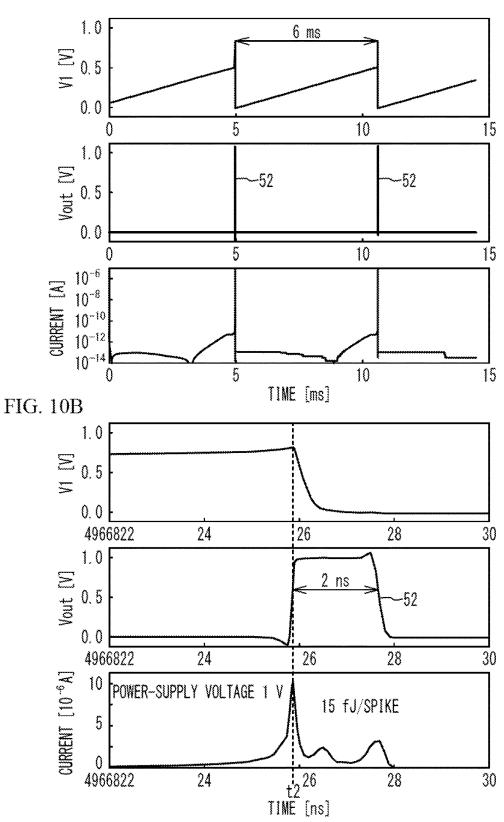

FIG. 10A and FIG. 10B illustrate an input voltage, an output voltage, and a consumption current with respect to time in the third embodiment. FIG. 10B is an enlarged view around the spike signal 52 in FIG. 10A. As illustrated in FIG. 10A, from time 0 ms to time 5 ms, the voltage V1 of the node 45 N1 gradually increases, and when the voltage V1 reaches 0.5 V, the voltage V1 rapidly increases to 0.8 V, and then becomes 0 V. At time 5 ms, the voltage Vout of the output terminal Tout becomes 1 V, and the spike signal 52 is output. The consumption current is  $10^{-11}$  A or less during the time 50 period from time 0 ms to time 5 ms.

As illustrated in FIG. 10B, at time t2, the voltage V1 of the node N1 rapidly decreases from 0.8 V to 0 V. The spike signal 52 with a width of approximately 2 ns is output to the output terminal Tout. At time t2, the current becomes 55 approximately  $1 \times 10^{-6} \text{ A}$  and largest. In the spike generation circuit 104, most of the power is consumed when the spike signal 52 is generated. When the power-supply voltage is 1 V, the consumption energy per spike is approximately 15 fJ. As seen above, the power consumption (the consumption 60 energy) for spike generation can be made to be very small.

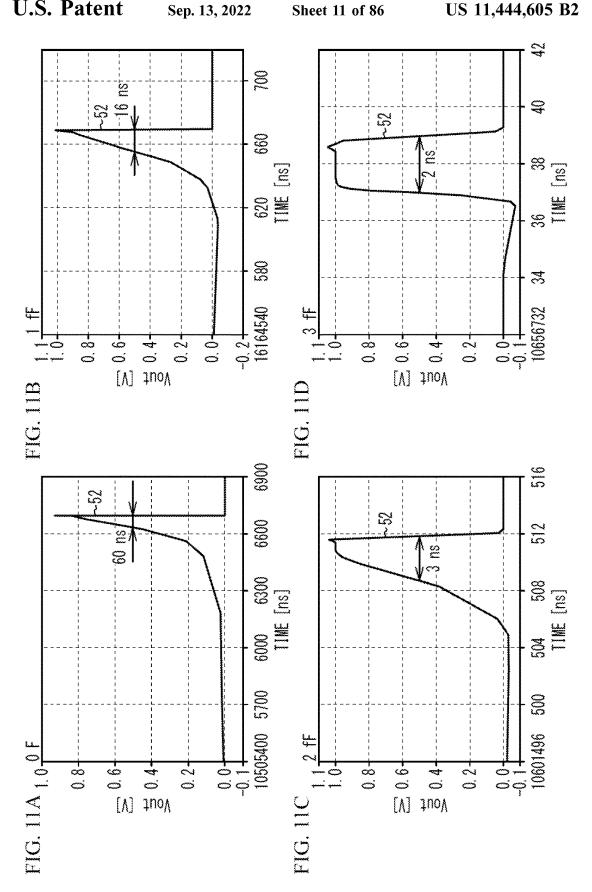

A description will be given of the function of the capacitor C2 in the third embodiment. The output voltage Vout with respect to time was simulated for different capacitance values of the capacitor C2 in the third embodiment. FIG. 65 11A to FIG. 12D illustrate the output voltage with respect to time in the third embodiment. The capacitance value of the

18

capacitor C2 in FIG. 11A to FIG. 12D is 0 F, 1 fF, 2 fF, 3 fF, 4 fF, 6 fF, 10 fF, and 20 fF, respectively.

As illustrated in FIG. 11A, when the capacitor C2 has a capacitance value of 0 F, the width of the spike signal 52 is approximately 60 ns, and the rise is gradual. As illustrated in FIG. 11B, when the capacitor C2 has a capacitance value of 1 fF, the width of the spike signal 52 is smaller, approximately 16 ns, and the rise is slightly steeper. As illustrated in FIG. 11C, when the capacitor C2 has a capacitance value of 2 fF, the width of the spike signal 52 is even smaller, approximately 3 ns, and the rise is even steeper. As illustrated in FIG. 11D, when the capacitor C2 has a capacitance value of 3 fF, the width of the spike signal 52 is smallest, approximately 2 ns, and the rise is even steeper.

As illustrated in FIG. 12A, when the capacitor C2 has a capacitance value of 4 fF, the width of the spike signal 52 is smallest, approximately 2 ns, and the rise is even steeper. As illustrated in FIG. 12B, when the capacitor C2 has a capacitance value of 6 fF, the width of the spike signal 52 is slightly larger, approximately 2.5 ns, the rise is approximately the same, and the fall is slightly more gradual. As illustrated in FIG. 12C, when the capacitor C2 has a capacitance value of 10 fF, the width of the spike signal 52 is even larger, approximately 3 ns, and the rise is slightly more gradual. As illustrated in FIG. 12D, when the capacitor C2 has a capacitance value of 20 fF, the width of the spike signal 52 is even larger, approximately 5 ns, and the rise and the fall are slightly more gradual.

As seen above, the provision of the capacitor C2 can narrow the width of the spike signal 52 and steepen the rise and the fall. Therefore, the power consumption is further reduced. The gate capacitance values of the NFET and the PFET are 0.1 fF, and the capacitance value of the capacitor C2 is preferably equal to or greater than 1 time, more preferably equal to or greater than 2 times, further preferably equal to or greater than 3 times the gate capacitance value. The capacitance value of the capacitor C2 is preferably equal to or less than 1000 times, more preferably equal to or less than 50 times the gate capacitance value.

FIG. 13A to FIG. 13D are diagrams for describing the function of the capacitor C2. FIG. 13A schematically illustrates a current flowing through the output node when the output of the inverter is inverted, with respect to time. As illustrated in FIG. 13A, when the output of the CMOS inverter is inverted, a low current IL flows to the output node. Thereafter, a high current IH flows. To give further details, the output current of the inverter in the previous stage is small at first and then increases. In other words, before the voltage of the input node of the inverter in the previous stage reaches the threshold voltage, a current flows a little, and when the voltage of the input node reaches the threshold voltage, the current flows all at once. Assuming that the currents IL and IH are constant, the time period during which the current IL flows is represented by TL, and the time period during which the current IH flows is represented by TH.

FIG. 13B to FIG. 13D schematically illustrate the voltage V4 of the node N4 with respect to time in the third embodiment. As illustrated in FIG. 13B, when the capacitance value of the capacitor C2 is small, the increase in the voltage of the node N4 depends on the time for the gate capacitance value of the inverter 22b to be charged. During the time period TL, the current IL is low. Thus, the voltage V4 of the node N4 gradually increases during the period TL. During the time period TH, the current IH is high. Thus, the voltage V4 rapidly increases. When the voltage V4 exceeds the threshold voltage Vth in the time period TL, the inverter

22b gradually inverts. Since the input current is small, the inverter 22b gradually inverts. This makes the rise and fall of the spike signal 52 gradual. In addition, when the capacitance value of the capacitor C2 is small, the timing of negative feedback is too early, preventing the positive feedback, which results in a further gradual rise.

As illustrated in FIG. 13C, when the capacitance value of the capacitor C2 is medium, the current IL is accumulated in the capacitor C2 in addition to the gate capacitance of the inverter 22b. Thus, the voltage V4 does not exceed the 10 threshold voltage Vth during the time period TL. When the voltage V4 exceeds the threshold voltage Vth in the time period TH, the output of the inverter 22b rapidly inverts. Therefore, the rise and fall of the spike signal 52 steepen.

As illustrated in FIG. 13D, when the capacitance value of the capacitor C2 is large, the rise of the voltage V4 during the period TH is gradual. Therefore, the output of the inverter 22b gradually inverts. Thus, the rise and fall of the spike signal 52 become gradual. Furthermore, the width of the spike signal 52 widens.

As described above, in the third embodiment, the provision of the capacitor C2 can narrow the width of the spike signal 52 and steepen the rise and fall of the spike signal 52. Therefore, the power consumption can be reduced.

A MOS capacitor or a metal insulator semiconductor 25 (MIS) capacitor can be used as the capacitor C2. The parasitic capacitance of the MOSFET may be used as the capacitor C2.

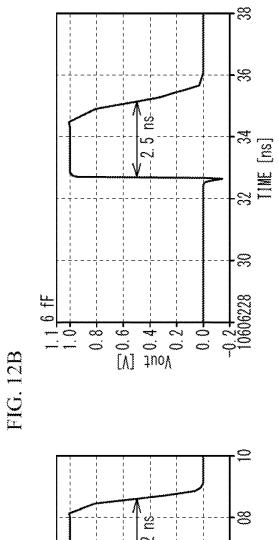

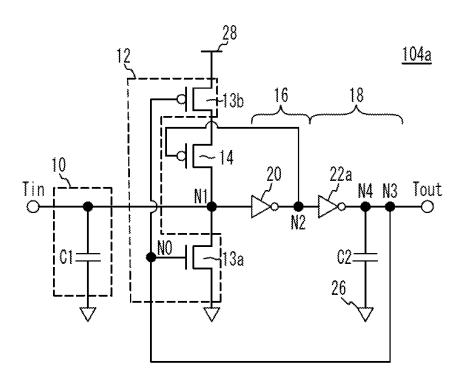

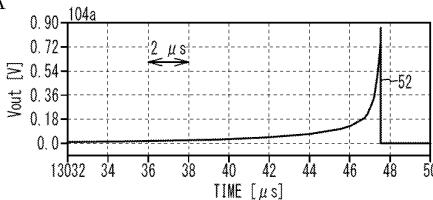

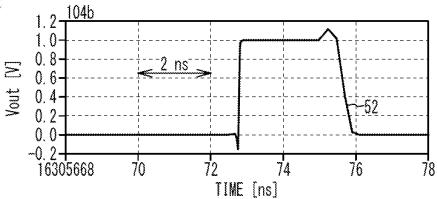

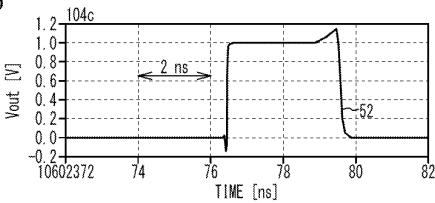

A simulation was conducted for different numbers of inverters in the inverting circuit **18** of the third embodiment. 30 FIG. **14A** to FIG. **15B** are circuit diagrams of spike generation circuits in the third embodiment. As illustrated in FIG. **14A**, in a spike generation circuit **104a**, the inverting circuit **18** includes one inverter **22a** and one capacitor C2. The capacitor C2 is coupled to the node N4 in the stage subsequent to the inverter **22a**. As illustrated in FIG. **14B**, in the spike generation circuit **104**, the inverting circuit **18** includes three inverters **22a** to **22**c as in FIG. **8** of the third embodiment. The capacitor C2 is coupled to the node N4 between the inverters **22a** and **22b**.

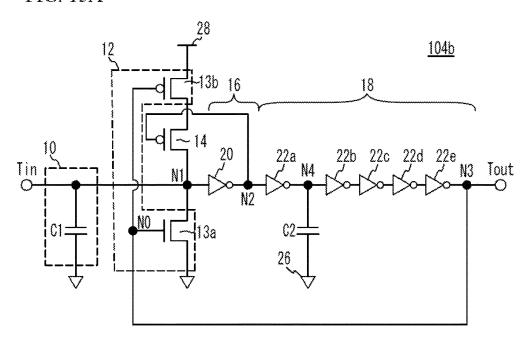

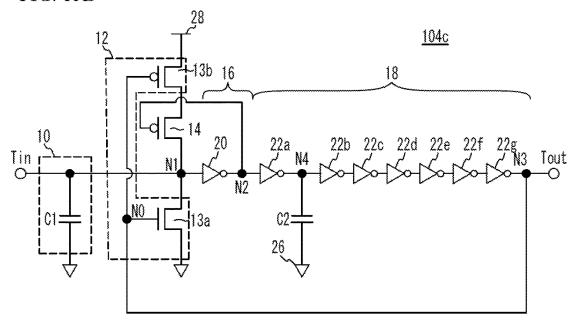

As illustrated in FIG. 15A, in a spike generation circuit 104b, the inverting circuit 18 includes five inverters 22a to 22e. The capacitor C2 is coupled to the node N4 between the inverters 22a and 22b. As illustrated in FIG. 15B, in a spike generation circuit 104c, the inverting circuit 18 includes 45 seven inverters 22a to 22g. The capacitor C2 is coupled to the node N4 between the inverters 22a and 22b.

FIG. 16A to FIG. 16D illustrate the output voltage of the spike generation circuit with respect to time in the third embodiment. As illustrated in FIG. 16A, in the spike generation circuit 104a, the rise of the spike signal 52 is gradual, and the width of the spike signal 52 is wide. As illustrated in FIG. 16B, in the spike generation circuit 104, the rise of the spike signal 52 is steeper, and the width of the spike signal 52 is approximately 2 ns. As illustrated in FIG. 16C, 55 in the spike generation circuit 104b, the width of the spike signal 52 is slightly wider, but the rise is steep. As illustrated in FIG. 16D, in the spike generation circuit 104c, the width of the spike signal 52 is slightly wider, but the rise is steep.

As apparent from above, the spike generation circuit is 60 achieved by adjusting the number of inverters in the inverting circuit 18 to be an odd number. If the number of the inverters in the circuit between the nodes N2 and N3 is an even number, the same level as that of the node N2 is output to the node N3. Therefore, in this case, the circuit between 65 the nodes N2 and N3 does not operate as the inverting circuit. The number of the inverters in the inverting circuit

20

18 is adjusted to be an odd number. To narrow the width of the spike signal 52 and steepen the rise and fall of the spike signal 52, the number of the inverters 22a to 22g is preferably three or greater. The number of the inverters 22a to 22g is more preferably three.

[Variation 1 of the Third Embodiment]