(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12)特許公報(B2)

(11)特許番号

特許第6778957号 (P6778957)

(45) 発行日 令和2年11月4日(2020.11.4)

(24) 登録日 令和2年10月15日(2020.10.15)

FLHO1L 21/28 (2006, 01) HO1L 21/28 301R

> HO1L 21/28 301B

> > 請求項の数8 (全 11 頁)

(21) 出願番号 特願2018-536911 (P2018-536911)

(86) (22) 出願日 平成29年2月23日 (2017.2.23)

(86) 国際出願番号 PCT/JP2017/006776

(87) 国際公開番号 W02018/042707

(87) 国際公開日 平成30年3月8日(2018.3.8) 令和1年12月6日 (2019.12.6) 審査請求日

(31) 優先権主張番号 特願2016-170939 (P2016-170939)

(32) 優先日 平成28年9月1日(2016.9.1)

(33) 優先権主張国・地域又は機関

日本国(JP)

||(73)特許権者 503360115

国立研究開発法人科学技術振興機構

埼玉県川口市本町四丁目1番8号

|(74)代理人 110002871

特許業務法人サカモト・アンド・パートナ

- Z

||(74) 代理人 100117444

弁理士 片山 健一

(72) 発明者 鳥海 明

東京都文京区本郷七丁目3番1号 国立大

学法人東京大学内

(72) 発明者 西村 知紀

東京都文京区本郷七丁目3番1号 国立大

学法人東京大学内

最終頁に続く

(54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

### 【請求項1】

室温におけるバンドギャップが 1 . 2 e V 以下の n 型導電型を有する半導体結晶の表面 に、電子濃度が 1 × 1 0 <sup>2 2</sup> c m <sup>3</sup> 未満の材料から成るコンタクト層が直接設けられて いるコンタクト構造を備えており、前記半導体結晶の表面領域のドナー濃度が1×10<sup>1</sup> <sup>8</sup> c m <sup>- 3</sup> 以下である、半導体装置。

# 【請求項2】

前記半導体結晶は、Si、Ge、もしくはSiとGeの化合物(SixGey)の何れ かである、請求項1に記載の半導体装置。

### 【請求項3】

前記半導体結晶はGeであり、前記コンタクト層はGd、Y、Ho、Er、Ybの何れ かのゲルマニウム化物もしくはBiを主成分とする材料から成る、請求項1に記載の半導 体装置。

前記半導体結晶はSiであり、前記コンタクト層はBiを主成分とする材料から成る、 請求項1に記載の半導体装置。

#### 【請求項5】

前記コンタクト層の上に金属層を備えている、請求項1~4の何れか1項に記載の半導 体装置。

【請求項6】

20

前記半導体装置は、前記半導体結晶がSiもしくはGeである、nチャネルMOSFETである、請求項1~5の何れか1項に記載の半導体装置。

#### 【請求項7】

室温におけるバンドギャップが1.2eV以下のn型導電型を有する半導体結晶の表面に、電子濃度が1×10<sup>22</sup> cm<sup>3</sup> 未満の材料から成るコンタクト層が直接設けられているコンタクト構造を備えており、前記半導体結晶はGeであり、前記コンタクト層はGd、Y、Ho、Er、Ybの何れかのゲルマニウム化物もしくはBiを主成分とする材料から成る、半導体装置。

#### 【請求項8】

室温におけるバンドギャップが1.2eV以下のn型導電型を有する半導体結晶の表面に、電子濃度が1×10<sup>22</sup>cm<sup>3</sup>未満の材料から成るコンタクト層が直接設けられているコンタクト構造を備えており、前記半導体結晶はSiであり、前記コンタクト層はBiを主成分とする材料から成る、半導体装置。

【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、n型導電型を有する半導体結晶の表面に設けられるオーミック性の高い接触の(低いショットキー障壁 Rを持つ)コンタクト構造に関する。

#### 【背景技術】

#### [0002]

半導体装置(デバイス)には電極が必須であり、半導体表面とのオーミック性接触を実現して、コンタクト抵抗を極力下げる必要がある。このためには、通常以下の二種類の方法がとられる。第一の方法は、半導体側の不純物濃度を上げて、金属中の電子がトンネル効果を通じて半導体側に出入りする状況を構築するものである。第二の方法は、電極の材料として、半導体材料表面にオーミック接触することができるような仕事関数を有する材料を選択するものである。

# [0003]

しかし、半導体結晶の導電型がn型の場合、仮に理論上はオーミック接触するはずの仕事関数を有する金属を選択しても、多くの場合、ショットキー接触してしまうことが知られている。この現象は、いわゆる「フェルミレベルピンニング」によるものと考えられている。

#### [0004]

# [0005]

n型半導体と電極材料との接合界面におけるコンタクト抵抗率  $_{C}$  は、ショットキー障壁  $_{B}$  および接合界面領域の単位体積あたりのドナー濃度  $_{D}$  と、下式 1 の関係にある。なお、式中の は定数である。

# [0006]

10

20

30

#### [0007]

つまり、 n 型半導体と電極材料とのオーミック接合界面を形成し、コンタクト抵抗率 c を下げるためには、ショットキー障壁 B を低くするか、接合界面領域のドナー濃度 N p を高くすればよい。

#### [00008]

しかし、接合界面領域のドナー濃度  $N_D$  を高くするには熱平衡状態では固溶限という限界があり、通常はその固溶限近くまで濃度は上げられており、それ以上に高くすることはできない。一方で、上述のとおり、N 型半導体の場合は特に、フェルミレベルピンニング現象により、ショットキー障壁 N を所望の程度にまで充分低くすることができない。

### [0009]

さらに、半導体素子の微細化に伴ってコンタクトの面積も小さくなり、上式 1 から容易にわかるように、コンタクト面積をSとすると実際のコンタクト抵抗Rcは c/Sとなり、同じ cを用いた場合でも微細化と共に急激に上昇することになり、半導体素子本来の性能向上を実効的に妨げることになる。つまり、半導体素子を微細化してもドレイン電極・ソース電極間全抵抗に対するコンタクト抵抗の割合を増やさないためには、 cそのものを縮小することが強く求められている。

#### [0010]

そこで、先に述べたように n 型半導体と電極材料との接合界面領域に高いドナー濃度 N D を有する半導体層を設けることでオーミック接触を実現する試みもなされてきた (特許 文献 1 : 特開 2 0 1 2 - 1 2 4 4 8 3 号公報や特許文献 2 : 特開 2 0 1 4 - 4 1 9 8 7 号 公報を参照)。

#### [0011]

# 【先行技術文献】

#### 【特許文献】

# [0012]

【特許文献 1 】特開 2 0 1 2 - 1 2 4 4 8 3 号公報

【特許文献2】特開2014-41987号公報

# 【非特許文献】

#### [0013]

【非特許文献 1】V. Heine, "Theory of Surface States," Phys. Rev. 138, A1689 (1965)

【非特許文献 2 】S. M. Sze, Physics of Semiconductor Devices, 2nd ed. Wiley, New York (1981)

【非特許文献 3】H. B. Michaelson, J. Appl. Phys. 48, 4729 (1977).

# 【発明の概要】

【発明が解決しようとする課題】

# [0014]

しかし、特許文献 1 や特許文献 2 に開示の手法のように、 n 型半導体と電極材料との接合界面領域に高いドナー濃度  $N_D$  を有する半導体層を設ける場合には、上記高ドナー濃度の半導体層を形成するための工程が必要となるため、半導体デバイスの製造コストの上昇を招く結果となる。さらに、熱平衡状態で実現される固溶限以上のドナーを半導体中に導

10

20

30

40

入することによって、新たな欠陥が導入されることになる場合が多く、n+/p接合の逆バイアスリーク電流が著しく増大することが危惧される。

#### [0015]

よって、 n 型半導体側の接合界面領域に新たな半導体層をわざわざ設けるのではなく、 n 型半導体の表面に接合される電極材料の選択そのものにより、オーミック性の高い接触を実現することが望ましい。また、 n 型半導体側の接合界面付近の高濃度のドナー層の配置に加えて、 Bの小さな電極を実現することで、上式 1 に従ってコンタクト抵抗率を大きく減少させることができることが期待される。

#### 【課題を解決するための手段】

#### [0016]

上述した課題を解決するために、本発明に係る半導体装置は、室温におけるバンドギャップが 1.2 e V以下の n 型導電型を有する半導体結晶の表面に、電子濃度が  $1 \times 10^{-2}$  c m  $^{-3}$  未満の材料から成るコンタクト層が直接設けられているコンタクト構造を備えていることを特徴とする。

#### [0017]

好ましくは、前記半導体結晶は、Si、Ge、もしくはSiとGeの化合物(Si $_{\times}$ Ge $_{\vee}$ )の何れかである。

#### [0018]

ある態様では、前記半導体結晶はGeであり、前記コンタクト層はGd、Y、Ho、Er、Ybの何れかのゲルマニウム化物もしくはBiを主成分とする材料から成る。

#### [0019]

また、ある態様では、前記半導体結晶はSiであり、前記コンタクト層はBiを主成分とする材料から成る。

#### [0020]

# [0021]

本発明に係る半導体装置が備えるコンタクト構造は、前記コンタクト層の上に金属層を 備えている態様とすることもできる。

#### [0022]

本発明に係る半導体装置は、前記半導体結晶がSiもしくはGeである、nチャネルMOSFETである。

### 【発明の効果】

# [0023]

本発明によれば、室温におけるバンドギャップが1.2eV以下のn型導電型を有する半導体結晶の表面に、電子濃度が $1 \times 10^{2}$ 2 c  $m^{-3}$  未満の材料から成るコンタクト層を直接設けることとしたので、コンタクト層側から半導体表面側への波動関数の浸み出しが抑制され、その結果、フェルミレベルピンニング現象に起因する障壁 B の発生が抑制され、オーミック性の高い接触を実現することができる。

### 【図面の簡単な説明】

# [0024]

【図1】成膜後の積層状態(A)および熱処理後の積層状態(B)を概念的に説明するための図である。

【図2】元素金属 / n - G e 接合の J - V 特性 (A) および金属ジャーマナイド / n - G e 接合の J - V 特性 (B) を示す図である。

【図3】G d ジャーマナイド / n - G e 接合および H o ジャーマナイド / n - G e 接合について、飽和電流密度 J 。の温度依存性からショットキー障壁(q ・ b )とその均一性

10

20

30

40

について調べた結果を示す図である。ここでqは電子のもつ電荷量である。

- 【図4】FLP緩和の程度のn-Geの結晶面方位依存性を調べた結果を示す図である。

- 【図5】コンタクト層として用いた材料毎のショットキー障壁の高さの測定値である。

- 【図 6 】 B i 系材料 / n S i 接合界面における F L P の緩和について調べた結果を示す図である。

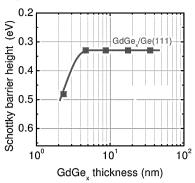

- 【図7】Gdジャーマナイド/n-Ge接合におけるショットキー障壁高さの、コンタクト層としてのGdジャーマナイド(GdGe<sub>x</sub>)の厚み依存性を調べた結果を示す図である。

【発明を実施するための形態】

[0025]

以下に、図面を参照して、本発明に係るコンタクト構造について説明する。

[0026]

上述したとおり、SiやGeといった代表的な半導体結晶を用いて半導体装置を作製するに際して、オーミック性の高い接触のコンタクト構造を設ける場合、電極として用いる金属材料の仕事関数を変えても、フェルミレベルピンニング現象により、所望のオーミック性を実現することが困難であり、この困難さは特に、n型の導電型の半導体結晶において顕著である。

[0027]

なお、半導体のバンドギャップが大きい場合には、斯かる現象は然程、顕著なものとはならない。よって、n型で且つ室温におけるバンドギャップが概ね1.2 e V以下の半導体結晶にオーミック性の高い接触を実現するに際し、フェルミレベルピンニング現象を如何に抑制するかが現実的な課題となってくる。

[0028]

本発明者らは、この問題を解決するに当たり、コンタクト層側から半導体結晶側への電子(波動関数)の浸み出しを抑制することで、フェルミレベルピンニングの影響を顕著に抑えることができるのではないかと考え、本発明を成すに至った。

[0029]

フェルミレベルピンニングの起源に関しては多くの議論があるが、いずれの場合においても界面ダイポール層が形成され、その大きさはダイポール密度と各ダイポールの強さによって決定されると考えられる。V. Heineの半導体界面の準位に対する議論に基づいて、その後、フェルミレベルピンニング現象を説明するために、金属誘起準位理論(Metal Induced Gap States: MIGSモデル)が提唱されている(非特許文献 1: "Theory of Surface States," Phys. Rev. 138, A1689 (1965))。

[0030]

このMIGS理論では、異なるバンド構造をもつ金属と半導体の接合界面における波動関数の整合性(フェルミ面の整合性)を問題とする。金属と半導体との接合界面にはバンドギャップの非整合性が生じるから、金属の波動関数はバンドギャップ中で減衰する。具体的には、接合界面に存在するポテンシャル障壁中において、波動関数(正弦波)が指数関数的に減衰することとなり、換言すれば、半導体のバンドギャップ中に、金属の波動関数が染み出した状態となる。そして、この波動関数の染み出しの程度が大きい程、フェルミレベルピンニング現象が顕著になる。

[0031]

本発明者らは、上記MIGS理論に基づけば、上述の波動関数の染み出しの程度を顕著に低く抑えることとすれば、フェルミレベルピンニング現象も顕著に抑制され、オーミック性の高い接触を容易に得ることが可能になると考えた。

[0032]

そして、波動関数の染み出しの程度を顕著に低く抑えるには、コンタクト層として用いる材料中の電子濃度を低く設計することが効果的であるとの知見に至った。

[0033]

本発明者らの単純な自由電子モデルでの計算によれば、コンタクト層と半導体のバンド

10

20

30

40

ギャップが所定の値である場合、コンタクト層側からの半導体結晶側への波動関数の染み出し量( $n_{transfer}$ )は、コンタクト層として用いる材料中の自由電子濃度(n)の1/3~2/3乗に比例する( $n_{transfer}$   $n^{1/3}$   $n^{2/3}$  )。一般的な金属材料中の電子濃度は10 $^{2/2}$  ~10 $^{2/3}$  cm  $n^{3/3}$  であるから、コンタクト層として用いる材料中の電子濃度を低く設計することにより、コンタクト層側からの半導体結晶側への波動関数の染み出し量を顕著に抑制することが可能となる。そこで、本発明者らは、このような条件を満足する材料として、従来の金属ではなく、当該半導体と金属の化合物(Geの場合にはジャーマナイド、Siの場合にはシリサイド)、あるいは半金属や導電性酸化物といった導電性を有する材料に注目することとしたのである。

[0034]

10

20

そして、本発明者らの検討によれば、室温におけるバンドギャップが 1.2 e V以下の n 型導電型を有する半導体結晶の表面に直接設けるコンタクト層の材料として、電子濃度 が  $1 \times 10^{-2}$  c m  $^{-3}$  未満の導電性を有する材料を選択すると、オーミック性の高い接触特性を示すコンタクト構造が得られるとの結果が得られた。

#### [0035]

ここで、本明細書中では、異種材料の接合領域において、 - 0 . 5 Vから + 0 . 5 Vの 範囲で電圧を変化させたときに電流が ± 1 0 %の範囲で線形に変化するものを、「オーミック性の高い接触」と定義する。

#### [0036]

室温におけるバンドギャップが1.2eV以下の半導体結晶としては、Si、Ge、SiとGeの化合物(Si、Ge、)を例示することができる。

#### [ 0 0 3 7 ]

上述の半導体とコンタクト層材料の組合せとしては、半導体結晶がGeであり、コンタクト層がGd、Y、Ho、Er、Ybの何れかのゲルマニウム化物もしくはBiを主成分とする導電性を有する材料を例示することができる。

#### [0038]

また、半導体結晶がSiであり、コンタクト層がBiを主成分とする材料である組合せも例示することができる。

### [0039]

なお、半導体結晶の表面領域のドナー濃度が高く、コンタクト層との接合界面での電子濃度が十分に高いと、そもそもオーミック接触性を得ることはできるが、従来の構造のものでは、ドナー濃度が  $1\times 10^{-1/8}$  c m  $^{-3}$  以下といった低濃度の場合にはオーミック接触を得ることが困難であった。これに対し、本発明の構造においては、ドナー濃度が  $1\times 10^{-1/8}$  c m  $^{-3}$  以下といった低濃度の場合でもオーミック性の高い接触をとることができるから、このようなコンタクト層の設計あるいは選択はきわめて重要な技術になる。特に、高濃度層の実現が難しい場合でもこの効果が得られることは、デバイスへの適用範囲を大きく拡げることになる。

#### [0040]

このようなコンタクト構造は、上述のコンタクト層の上に金属層を備えている態様としてもよいことは言うまでもない。

40

# [0041]

このようなコンタクト構造を備える半導体装置は、例えば、半導体結晶がSiもしくは Geである、C-MOSにおけるnチャネルMOSFETであってよい。

# 【実施例】

#### [0042]

[金属ジャーマナイド/n-Ge接合界面におけるFLPの緩和]

上述のとおり、フェルミレベルピンニング(FLP)の起源に関しては多くの議論があるが、いずれの場合においても界面ダイポール層が形成され、その大きさはダイポール密度と各ダイポールの強さによって決定されると考えられる。

### [0043]

本実施例では、金属とGeの化合物を形成することによって電子濃度の低い金属を形成し、染みだし量を変化させることによって、ダイポールの強さと密度を変化させ、n-Geとの接合界面との間に生じるFLPについて系統的に調べた。

#### [0044]

ドナー濃度が  $10^{16}$  / c m  $^3$  レベルの n 型の ( 100 ) G e 基板上に、厚みが 30 n m の各種金属(G d、 H o、 E r、 Y b、 T i、 C o、 P t )の膜を蒸着成膜し、その上にアモルファス G e の膜を 20 n m の厚みで蒸着成膜した。その後、真空中(概ね  $10^{5}$  P a 程度)で、 500 で 30 分間の熱処理を行い、金属 - G e 化合物 / n - G e 接合を形成した。これらの各試料は何れも、 X 線回折法により、上記熱処理により多結晶ジャーマナイドが形成されていることが確認されている。なお、比較のために、上記各金属の成膜のみを行い、熱処理を行わない試料も作製した。そして、これらの試料につき、接合界面のショットキー特性を評価した。

#### [0045]

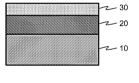

図 1 は、上記成膜後の積層状態(図 1 ( A ))および熱処理後の積層状態を概念的に説明するための図(図 1 ( B ))である。成膜後には、 n 型の( 1 0 0 ) G e 基板 1 0 の表面上に、金属膜 2 0 とアモルファス G e の膜 3 0 が積層されていた状態にあったものが、 5 0 0 で 3 0 分間の熱処理後には、金属膜 2 0 とアモルファス G e の膜 3 0 が金属ジャーマナイド膜 4 0 となり、 G e 基板 1 0 の表面上に直接、金属ジャーマナイド膜 4 0 が接合された状態となる。

# [0046]

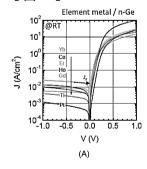

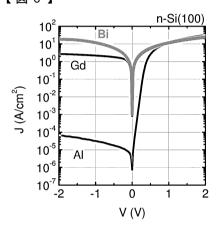

また、図 2 は、元素金属 / n - G e 接合の室温におけるJ・V特性(図 2 ( A ))および金属ジャーマナイド / n - G e 接合の室温におけるJ・V特性(図 2 ( B ))を示す図である。先ず、図 2 ( A )と図 2 ( B )との比較から、金属ジャーマナイド / n - G e 接合とすることにより、オーミック性が向上していることが明瞭に読み取れる。

#### [0047]

また、図 2 ( B )中に示した 7 種の金属ジャーマナイド / n - G e 接合を比較すると、相対的に低い仕事関数を有する金属(G d、H o、E r、Y b)より形成した金属ジャーマナイドにおける n - G e との接合において、オフ電流、飽和電流密度(J  $_s$ : V = 0 における J の外挿値)の増大が認められる。なお、上記 G d、H o、E r、Y b 以外にも、Y のジャーマナイド及び B i を主成分とする材料においても同様の効果が得られた。

#### [0048]

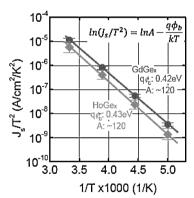

図 3 は、G d ジャーマナイド / n - G e (GdGex/n-Ge) 接合および H o ジャーマナイド / n - G e (HoGex/n-Ge) 接合について、飽和電流密度 J  $_s$  の温度依存性からショットキー障壁 (g・ $_b$ ) とその均一性について調べた結果を示す図である。

# [0049]

この図に示した温度依存性を示す直線の傾きから、ショットキー障壁(q ・  $_b$  )は、G d ジャーマナイド / n - G e 接合につき 0 . 4 2 e V 、H o ジャーマナイド / n - G e 接合につき 0 . 4 3 e V と見積もられる。また、この直線の切片より見積もられるリチャードソン定数は、非特許文献 2 にある値 1 4 3 A / c m  $^2$  / K  $^2$  にほぼ一致する。この事実は、局所的な障壁低下によるリークではなく均一にショットキー障壁が形成されていることを示している。

#### [0050]

これらの結果から、金属ジャーマナイド/n-Ge接合界面においては、形成されるダイポールの密度が減少し、その結果、FLPの緩和が起きているものと考えられる。

#### [0051]

[n-GeにおけるFLP緩和の面方位依存性]

図4は、上述のFLP緩和の程度の、n-Geの結晶面方位依存性を調べた結果を示す図である。試料として、(111)、(100)、(110)を主面とするn-Ge基板の上にGdジャーマナイドを設け、Gdジャーマナイド/n-Ge接合を形成した。

# [0052]

10

20

30

10

20

30

40

50

#### [0053]

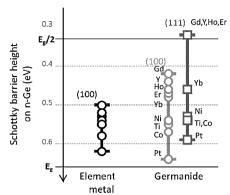

図 5 に、ショットキー障壁の高さの、n-Ge 基板上に設けたコンタクト層の材料依存性を整理した。図中の左側に、純粋な単元素金属材料のコンタクト層をn型Ge(100) 面上に設けた場合のショットキー障壁高さを示しており、図中の右側に、上記単元素金属のジャーマナイド(金属-Ge化合物)からなるコンタクト層を、n型Ge(100) 面上およびn型Ge(111) 面上に設けた場合のショットキー障壁高さを示している。上述のとおり、金属材料でコンタクト層を設けた場合に比較して、ジャーマナイド化した材料から成るコンタクト層を設けた場合には、ショットキー障壁が低くなる傾向が明瞭に読み取れる。また、n-Ge を基板の主面が(111)の場合には、主面が(100)の場合に比較して、ショットキー障壁が低くなる傾向がある。

#### [0054]

「Bi系材料/n-Si接合界面におけるFLPの緩和]

図6は、半導体結晶をn-Geに代えてn-Siとした場合の、Bi系材料/n-Si接合界面におけるFLPの緩和について調べた結果を示す図である。この図で示したn-Siの面方位は(100)で、このSi基板の上にコンタクト層としてBiを設け、Bi/n-Si接合を形成した。なお、比較のために、Gd/n-Si接合およびAl/n-Si接合についても試料作製した。

#### [0055]

図6に示した室温におけるJ・V特性から、Alコンタクト層、Gdコンタクト層、Biコンタクト層の順に、接合界面におけるFLPの緩和が強くなっており、特に、Biコンタクト層(Bi/n-Si接合)の場合には略完全なオーミック性が得られている。

#### [0056]

これらの金属中の自由電子濃度は、A 1 において  $2 \times 1$  0 2 3 c m  $^{-3}$  、G d において  $6 \times 1$  0  $^{2}$  3 c m  $^{-3}$  、B i において 1 0  $^{16}$  ~ 1 0  $^{17}$  c m  $^{-3}$  であり、一方で仕事関数に関してはA 1 においては ~ 4 . 3 V、G d において 3 . 1 V、B i において 4 . 2 V の値が報告されている(非特許文献 3 参照)。B i とA 1 はほとんど同じ仕事関数をもつが、自由電子密度が低いB i では接合界面における F L P の程度が著しく弱くなり、ショットキー障壁の高さに関してB i はほぼ G d の場合かそれ以下の仕事関数の場合に近いことが明瞭に読み取れる。

### [0057]

# [コンタクト層の薄膜化]

図 7 は、G d  $\tilde{y}$   $\tilde{y}$

#### [0058]

上述したように、本発明によれば、室温におけるバンドギャップが1.2eV以下の n 型導電型を有する半導体結晶の表面に、電子濃度が1×10<sup>22</sup> c m <sup>3</sup> 未満の材料から成るコンタクト層を直接設けることとしたので、コンタクト層側から半導体表面側への波動関数の浸み出しが抑制され、その結果、フェルミレベルピンニング現象に起因する障壁。の発生が抑制され、オーミック性の高い接触を実現することができる。

#### [0059]

なお、本発明を実施するに際し、上記コンタクト層の上に金属層を備えている態様とす

10

ることができることは言うまでもない。

### [0060]

本発明に係るコンタクト構造は、 C - M O S をはじめとする半導体装置において極めて 有用である。

【産業上の利用可能性】

# [0061]

本発明によれば、コンタクト層側からn型半導体表面側への波動関数の浸み出しが抑制され、その結果、フェルミレベルピンニング現象に起因する障壁 <sub>B</sub>の発生が抑制され、オーミック性の高い接触を実現することができる。

# 【符号の説明】

# [0062]

- 10 n型Ge基板

- 2 0 金属膜

- 30 アモルファスGeの膜

- 40 金属ジャーマナイド膜

(A)

-z-40 -z-10

(B)

【図2】

Germanide metal / n-Ge

@RT

GdGer

HoGer

Proger

Pro

【図3】

【図4】

(B)

# 【図5】

# 【図6】

# 【図7】

### フロントページの続き

特許法第30条第2項適用 (1)発行日:平成28年3月3日 刊行物:2016年第63回応用物理学会春季学術講演[講演予行集] 公益社団法人 応用物理学会 (2)開催日:2016年6月7日 集会名、開催場所:7th International Symposium on Control of Semiconductor Interfaces(ISCSI-VII) and International SiGe Technology and Device Meeting 2016(ISTDM2016)国立大学法人名古屋大学 野依記念学術交流館 カンファレンスホール (3)ウェブサイトの掲載日:2016年7月15日 ウェブサイトのアドレス http://iopscience.iop.org/article/10.7567/APEX.9.081201/meta;jsessionid=24562E61C5B95FA4D90ACD16B326A94C.c5.iopscience.cld.iop.org

# 審査官 佐藤 靖史

(56)参考文献 国際公開第2013/133060(WO,A1) 特開2009-05996(JP,A)

(58)調査した分野(Int.CI., DB名) H01L 21/28