# **Tunnel Transistor**

# **Tunnel Field-Effect Transistor (FET)** using III-V/Si Heterojunctions

#### Associate Prof. Katsuhiro Tomioka (Hokkaido University)

## **1.Introduction**

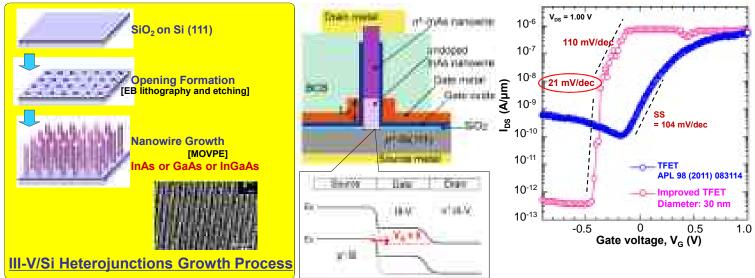

Conventinal MOSFETs have theoretical limit in subthreshold slope(SS) characteristics resulted from carrier diffusion (SS > 60mV/dec.). Our technology can realize steep-slope nanowire-based FET by controlling III-V/Si heterojunctions without misfit dislocations, which can be achieved with nano-heteroepitaxial methods.

## 2. Device Structure, Performance of the Tunnel FET

-The combination of a narrow band gap III-V with Si is a good system for boosting up the ON-state current and has high band-to-band tunneling efficiency.

-The subthreshold slope(SS) is far lower value than 60mV/dec.(theoretical limit value) of Si FET.

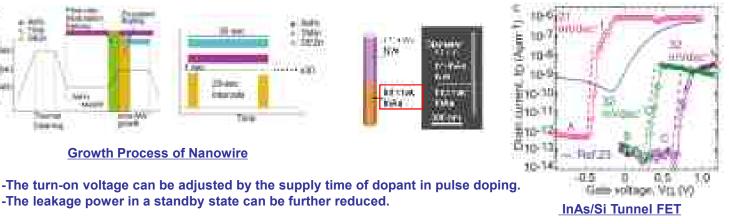

## 3. Synthesis of Nanowire by using Pulse Doping

-The leakage power in a standby state can be further reduced.

With respect to the impurity density of undoped InAs nanowire, supply the p-type dopant of the 10<sup>16</sup>cm<sup>-3</sup> to compensate for the n-type dopant once for x seconds, to make the electrically neutral intrinsic layer.

## 4. Application Examples

-Low voltage operation transistor -Low power consumption LSI -Sensing devices for IoT

#### 5. Patent Licensing Available

Patent No.: WO2011/040012, WO2015/022777 (US2016/0204224, JP, EP, CN, KR, TW) WO2015/064094 (US2016/0284536, JP, EP, CN, KR, TW) JST/ IP Management and Licensing Group Phone: +81-3-5214-8486 E-mail: license@jst.go.jp

http://www.jst.go.jp/tt/EN/