# Semiconductor Structure provided with AION Film on top of Ge Layer

#### 1. Abstract

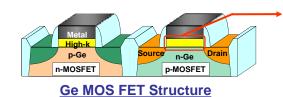

- By forming aluminum oxynitride on the Ge (Germanium) layer, high reliability thin film as the gate insulating film of MOSFET was realized.

- High-pressure inert gas post deposition annealing (PDA) using N<sub>2</sub> or Ar gas dramatically improved the electrical properties of AION/Ge MIS gate stacks.

#### 2. Ge MOSFET: Expectation, and Problems to be Solved

- Ge which has the higher carrier mobility, is a promising candidate as a channel material in the next generation of MOSFETs. In miniaturized MOSFETs, gate insulators with a high dielectric constant (high-k) are required in order to suppress the gate leakage current and the short channel effects.

- There is also a problem how good interface and insulating layer on Ge can be realized.

Gate Stack Ge-insulation film interface GeO<sub>2</sub> -High-k Interface **Problems:**

- Degrade carrier mobility

- Less reliability

- Variation increase

### 3. Scalable High-k/Ge Gate Stack Technology

- We investigated the use of aluminum oxynitride film (AION) as a gate insulating film formed on the Ge substrate. By using an AION film, a thin EOT (Equivalent Oxide Thickness) is possible.

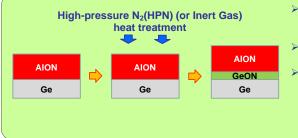

- However, heat treatment of AION film in order to improve the quality of the AION film deteriorates the interface between Ge substrate and the AION film.

After examining the conditions under which the interface between the AION film and the Ge substrate is not degraded by heat treatment, we tried to apply highpressure N<sub>2</sub> post-deposition annealing (HPN PDA) in order to suppress the N<sub>2</sub> desorption, which was analogous to high-pressure oxidation (HPO) annealing in GeO<sub>2</sub>/Ge stack.

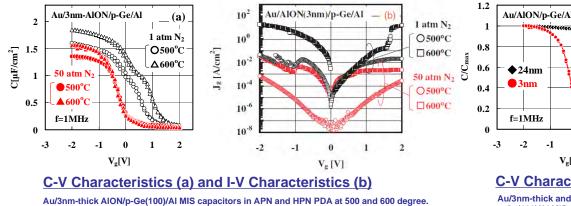

- HPN PDA dramatically improves the C-V characteristics, whereas the large interface states were observed in the same gate stack as a result of atmospheric-pressure N<sub>2</sub> (APN) post-deposition annealing.

- HPN PDA also reduces the gate leakage current.

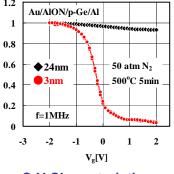

- HPN PDA only improves the interface in the case of thin AION/Ge.

#### **C-V Characteristics**

Au/3nm-thick and 24nm-thick AION/ p-Ge(100)/AI MIS capacitors in HPN PDA at 500degree for 5min.

## Patent Licensing Available

Patent No.: WO2014/030371

JST/ IP Management & Licensing Group Phone: +81-3-5214-8486, E-mail: license@jst.go.jp