## 半導体

研究開発課題名:性能バランスを最適設計した異種チャネル3D CFET SRAM

研究開発代表者:前田辰郎 産業技術総合研究所・先端半導体研究センター 研究チーム付

共同研究機関: Taiwan Semiconductor Research Institute (連携機関)

#### 目的:

低消費電力とセル面積の極限縮小を可能とする多積層型異種チャネルFETのプロセス開発を実施し、性能バランスを最適化設計した3D CFET SRAM(低消費電力な半導体メモリ)の実現と高性能化を目指す。

#### 研究概要:

## ・取り組む課題

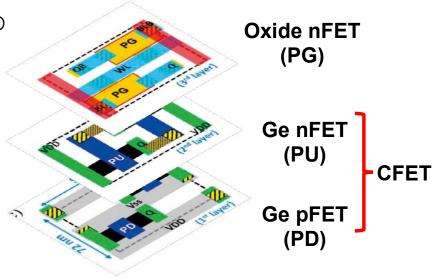

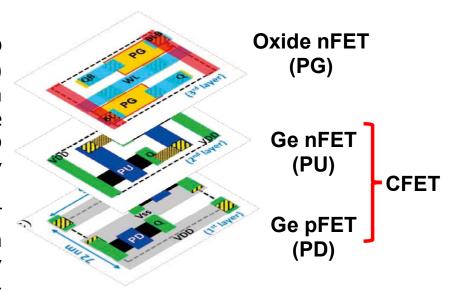

SRAMのインバータを、低消費電力化が可能なGe CFETに置き換え、アクセストランジスタであるPGも積層型の酸化物nFETにすることで、セル面積を極限まで縮小し、メモリの大容量化を図る。

SRAMのリーク電流の増大、ソフトエラー率の上昇、ノイズマージンの減少という課題を、3次元集積化した異種チャネルCFET SRAM特有のDTCO(設計とテクノロジの協調最適化)によって解決する。

異種チャネル3D CFET SRAM

## カーボンニュートラル貢献へのシナリオ

1ビットあたりの消費電力を現在の2nm世代SRAMと比較して70%まで低減させ、データセンタなどのエネルギー消費削減に貢献。

# **Semiconductor**

**R&D Project Title:**

Performance Balance Engineering for Hetero-integrate 3D CFET SRAM

Project Leader: Tatsuro MAEDA, Concurrent post

Semiconductor Frontier Research Center

National Institute of Advanced Industrial Science and Technology (AIST)

**R&D Team:** Taiwan Semiconductor Research Institute (TSRI)

#### **Summary:**

This project focuses on realizing performance-balanced 3D CFET SRAM (low power consumption semiconductor memory) with extremely scaled cell size and low leakage current through multiple stacked hetero-integrated channel technology. The specific Design Technology Co-Optimization (DTCO) for 3D CFET SRAM can be conducted through TCAD (Technology Computer Aided Design) simulation.

The power consumption per bit cell of the designed 3D CFET SRAM is expected to reduce by 70 % compared to the 2 nm node SRAM cell, which contributes to reducing energy consumption in data centers, etc., leading to a carbon-neutralized society.

**Hetero-integrate 3D CFET SRAM**