さきがけ 研究者

研究課題名

計算科学的手法による省電力・低損失デバイス用界面のデザイン

プロフィール

Tomoya Ono

1974年 岡山県生まれ。2001年 大阪大学大学院工学研究科 博士課程修了、博士(工学)。2000年 日本学術振興会 特別研究員(DC2)。2001年 大阪大学大学院工学研究科 助手(2007年より助教)。2014年 筑波大学計算科学研究センター 准教授、現在に至る。

2007年 ドイツAlexander von Humboldt 研究員(ユーリッヒ研究センター)。

研究分野:第一原理計算、電子デバイス

趣味:旅行

- ※プロフィールは、終了時点のものです。

研究内容紹介

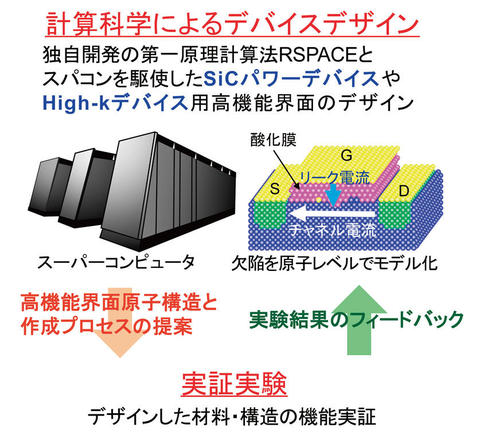

近年の人類の生活環境の変化を鑑みれば、デバイスの省電力化は緊喫の課題です。デバイスの電力消費を削減するには、移動度の高いチャネル材料や誘電率の高い絶縁材料の利用に加え、チャネル電流やリーク電流などの電子(キャリア)の流れを理想的に制御することが必要です。たとえば、電力機器用の低電力損失パワーデバイスとして期待されているSiCデバイスでは、キャリア移動度がSiC結晶の移動度に比して大幅に低く、Si結晶比で90%を大きく上回るSiデバイスに対して大きな欠点になっています。これは、絶縁膜/基板界面での欠陥でのキャリア散乱が原因と考えられています。また、ゲート酸化膜厚が2nm以下まで微細化されたナノエレクトロニクスデバイスでも、絶縁膜/基板界面の原子構造、とりわけ欠陥によって、キャリア移動度やリーク電流が支配されます。このように、界面欠陥が電子伝導に与える影響の理解と制御は、デバイスの省電力化に対して重要な課題です。

界面欠陥はデバイス全体のサイズから見れば稀にかつ偶然的に存在するため、実験的に意図した欠陥を作成してキャリア移動特性やリーク電流を測定し、デバイス性能に影響を与える欠陥とそうでない欠陥を区別することは容易ではありません。これに対し、量子力学の第一原理に基づいた計算法は、経験的なパラメータを持ち込むことなく、界面欠陥による電子状態や電子の伝導特性の変化を調べることができます。ここでは、これまで私が独自に開発してきた量子力学の第一原理電子状態・電気伝導特性計算コードRSPACEと京コンピュータに代表される超並列スーパーコンピュータを駆使し、第一原理計算を用いた電子デバイス界面の電子状態や伝導特性を評価・デザインする基盤技術を構築します。これを用いて、低電力損失パワーデバイスや省電力ナノエレクトロニクスデバイスの実現をめざし、デバイス用の界面原子構造と作成プロセスをデザインします。単一分子スケールの欠陥の振る舞いのみならず、界面欠陥を丸ごと含んだモデルによる解析により、半導体デバイスの絶縁膜/基板界面での原子レベルでの接合状態の違いがキャリア移動度やリーク電流といった伝導特性にどのような影響を及ぼすのかを電子素過程から調べます。

本研究では、(1)計算科学的手法によるデバイス界面構造の伝導特性を評価・デザインする基盤技術の構築、(2)デバイス性能を劣化させる界面欠陥の特定、(3)優れた絶縁性、キャリア移動度を持つ低電力損失パワーデバイスや超省電力エレクトロニクスデバイス用の界面原子構造と作成プロセスのデザイン、(4)デバイス作成研究者と連携したデザイン主導での機能実証を目標とします。