さきがけ 研究者

研究課題名

新しい半導体固相界面による新規グリーンデバイスの開発

プロフィール

Katsuhiro Tomioka

1980年群馬県生まれ。2003年 群馬大学工学部電気電子工学科 卒業、2005年 同大大学院工学研究科 修士課程修了。2008年 北海道大学大学院情報科学研究科 博士課程修了、博士(工学)。2007年 日本学術振興会 特別研究員(DC2)、2008年 日本学術振興会 特別研究員(PD)。2009年 北海道大学 グローバルCOE研究員。2009年 科学技術振興機構 さきがけ「革新的次世代デバイスを目指す材料とプロセス」専任研究者。2015年より、北海道大学大学院情報科学研究科 助教、現在に至る。

研究分野:半導体工学、半導体結晶成長

- ※プロフィールは、終了時点のものです。

研究内容紹介

人口増加と科学技術の進歩にともなうエネルギー需要の高まりは、化石燃料を主とした社会・経済を疲弊させ、単純な科学技術の進歩が社会に大きく貢献できる機会を極端に少なくしています。そのような背景の中で、エネルギー高効率化には、エネルギーを効率良く"創る・貯める・使う"デバイスの総合的な技術革新が必要と考えています。

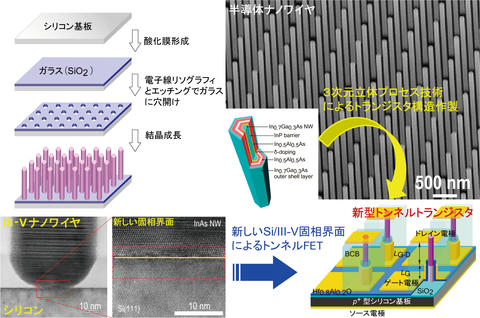

半導体トランジスタやその集積回路に代表される分野では、シリコン電界効果トランジスタ(FET)の集積技術の到達限界が指摘され始めています。特に、集積回路のチップ当たりの電力消費量の急増は深刻な課題となり、新材料・デバイス構造の導入・開発が検討されています。新材料・デバイス構造に期待される性能は、FETやその集積回路と同等かそれ以上であること、劇的な省エネルギー性が期待できることの2点に集約されます。特に省エネルギー性については、従来の金属-酸化物-半導体(MOS)FETのサブスレッショルド特性(SS)に理論限界(60mV/dec)があるため、この特性を下回り、低消費電力で動作するトンネルFETの研究・開発が急務となっています。現在の集積回路の駆動電圧(0.9V)以下、さらに0.3V以下で動作させるためには、SSが30mV/dec以下になるスイッチ特性を実現しなければならないからです。これを実現できるスイッチ素子の候補がトンネルFETですが、この素子は、トンネル障壁を介して電子の輸送しているため、スイッチングで得られる電流が従来のFETよりも小さくなる欠点があります。

本研究では、まず、従来のFETのキャリア輸送とは異なる原理を持つトンネルFETをSiとIII-V族化合物半導体一次元ナノ構造からなる固相界面を応用し作製します。次に、キャリアの受け手側で電子を良く輸送させる技術・構造を導入することで、これまでにない低消費・高速化トンネルトランジスタを作製します。この素子が実現し、シリコン集積回路に導入されると、既存の集積回路の性能よりも高性能な機能を有したまま、チップ当たりの電力密度を103W/cm2から10W/cm2以下に削減することができます。さらに、エレクトロニクス機器・車載機器で普及しているあらゆる分野の電子機器の消費電力を1/100にする要素技術を確立することができます。