# JST International Symposium on Dependable VLSI Systems 2012

Tokyo, Japan December 1, 2012

**浅井彰二郎** CREST/DVLSI 研究総括 (株)リガク取締役副社長 Shojiro Asai Research Supervisor, CREST/DVLSI Exec. VP and Director, Rigaku Corporation

Program term: FY2007~2014

The "<u>Dependable VLSI Systems</u>" is a collaborative university-industry research program funded by Japan Science and Technology Agency under the CREST\* framework.

- In its 6th year of the 8 year term

\*CREST: http://www.jst.go.jp/kisoken/crest/en/index.html

#### Attributes, Threats, and Means in Dependability as defined by IFIP:

| Attributes Availability Reliability Safety Integrity Maintainability | way to assess the dependability of a system readiness for correct service continuity of correct service absence of catastrophic consequences on the users/environment absence of improper system alteration ability for a process to undergo modifications and repairs |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Threats Fault Error Failure                                          | things that can affect the dependability of a system defect in a system discrepancy between the intended and actual behavior of a system system behavior that is contrary to its specification                                                                         |

| Means Prevention Removal Forecasting Tolerance                       | ways to increase a system's dependability preventing faults being incorporated into a system fault removal during development and removal during use prediction of faults to remove them or circumvent their effects putting fault-tolerant mechanisms in place        |

|                                                                      |                                                                                                                                                                                                                                                                        |

#### Rationale for research in DVLSI

**VLSI:** Is the component key to systems of all kinds.

Its dependability is at the foundation of

systems dependability.

**Problems:** The dependability of VLSI is actually

being increasingly more threatened.

.

### Threats arising from miniaturization

Variations in dimensions, shapes, doping densities,

Decrease in S/N ratio (radiation, EMI, fixed and floating charges),

Aggravating wear/fatigue phenomena (NBTI, hot carriers, electromigration).

## Threats arising from increased complexity

Enhanced functionality (id, encryption,---)

Multiple- Many-core architecture, multi-thread operation,

Heterogeneous integration Analog, digital, nonvolatile, network, sensors, actuators, etc.

### Mission of the DVLSI Program:

- Contain Rising Threats within VLSI (Component Supposed to be Most Dependable) by Design and/or Testing

- 2. Provide New Functionalities in VLSI which Improve Dependability at the Systems Level

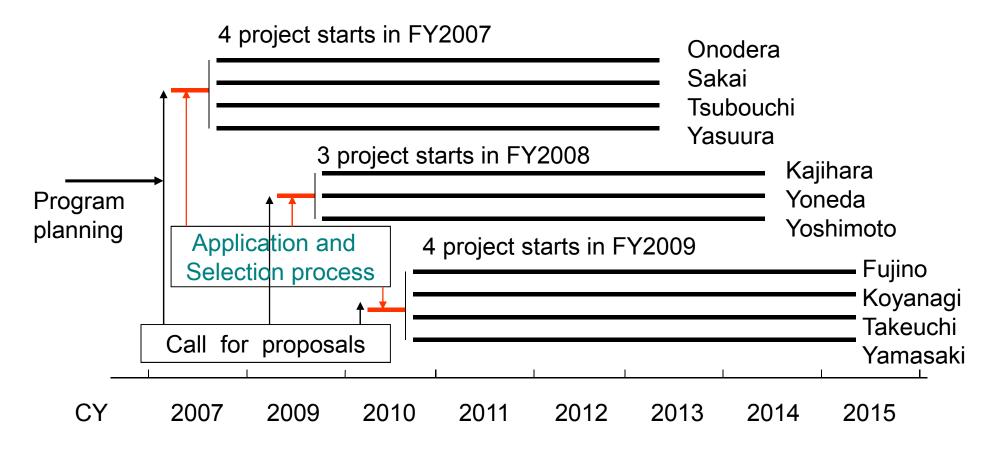

### Selection and Terms of the DVLSI Projects

Program Term: 2007- 2015

### **Applications eyed and Approaches taken**

| Application | Space Plant Control Robot Auto Information Finance Consumer                      |

|-------------|----------------------------------------------------------------------------------|

| Onodera     | Reconfigurable Processor, FF Design, Layout for Manufacturability                |

| Sakai       | Failure-Resistant Architecture, Formal Design Verification                       |

| Tsubouchi   | Wide Bandwidth RF, FDE, Coding,, Connectivity, Heterogeneous Interface           |

| Yasuura     | Systems-Level Soft-error Simulation, Soft-error-resistant Circuit/Systems Design |

| Kajihara    | Design/Test for Field Dependability                                              |

| Yoshimoto   | Soft-Error-Resistant Memory, Systems-Level Simulation                            |

| Yoneda      | Networked Multi-Core Systems                                                     |

| Koyanagi    | Dependable 3D Processor for Image-Recognition                                    |

| Takeuchi    | Wireless Solid-State Drive, Wireless Interconnect, Wireless Power                |

| Fujino      | Tamper-Resistant Circuits, Tamper-resistance test                                |

| Yamasaki ,  | Pool time OS, controller and packaging for Hard Deal Time applications           |

Real-time OS, controller, and packaging for Hard-Real-Time applications

VLSI JST/CREST Program 'Dependable VLSI Systems'

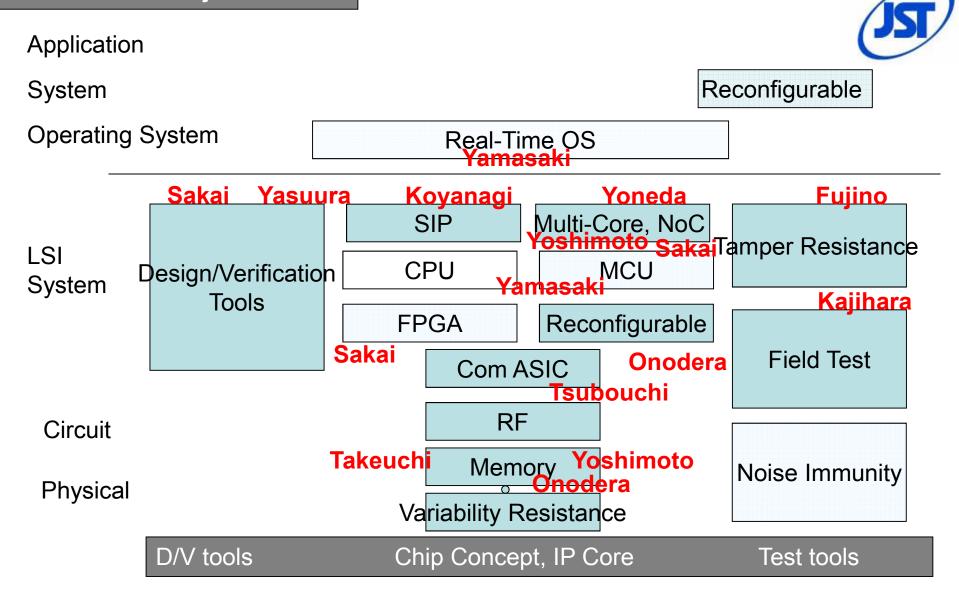

#### **Areas DVLSI Projects cover:**

9

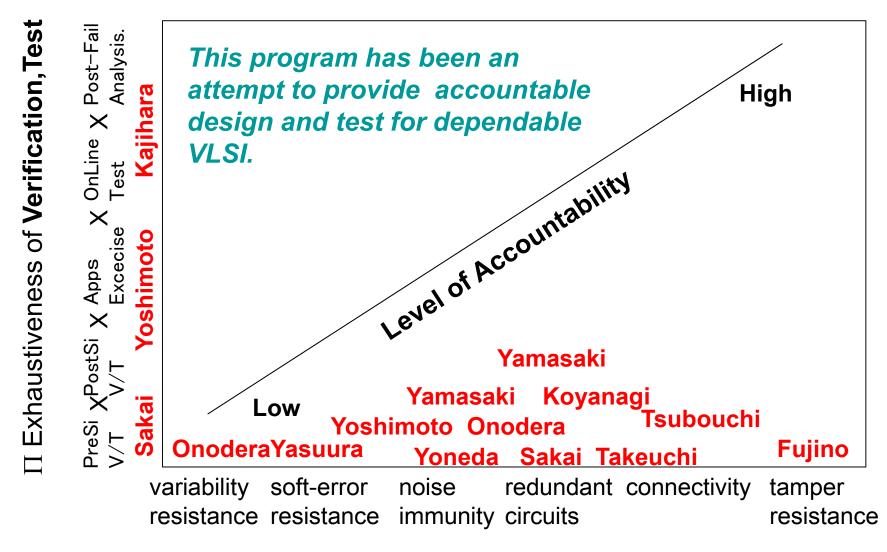

□ Strength of Means against Threat (Robustness of Technology)

10

#### Thanks to the Organizing Committee Members:

Chair: Hidetoshi Onodera (Kyoto University)

Secretary: Masanori Hashimoto (Osaka University)

Members: Mitsumasa Koyanagi (Tohoku University)

Masahiro Goshima (University of Tokyo)

Suguru Kameda (Tohoku University)

Hiroshi Oguma (Toyama National College of Technology)

Yusuke Matsunaga (Kyushu University)

本シンポジウムのプログラム委員会に感謝申し上げます。 小野寺先生、橋本先生、小柳先生、松永先生、亀田先生、五島先生、 小熊先生

#### Thanks to Advisors

Masatoshi Ishikawa (Professor, The University of Tokyo)

Tohru Kikuno (Professor, Osaka Gakuin University)

Tadayuki Takahashi (Professor, Japan Aerospace Exploration Agency)

Naoki Nishi (General Manager, NEC Corp., System IP Core Research Lab.)

Atsushi Hasegawa (Director, Renesas Electronics Corp.)

Toshio Masubuchi (Director, Toshiba Corp. Semiconductor & Storage Company)

Kazuo Yano (Senior Chief Researcher, Hitachi Ltd. Central Research Lab.)

Koichiro Takayama (Chief Researcher, Fujitsu Laboratory Ltd.)

DVLSI研究領域アドバイザーの方々に感謝申し上げます。

石川正俊 東京大学教授 菊野享 大阪学院大学教授 高橋忠幸 宇宙航空研究開発機構宇宙研究所教授 西直樹 日本電気(株)研究所長

長谷川淳 (株)ルネサスエレクトロニクス 執行役員技術開発本部長 増渕美生 (株)東芝セミコンダクター・ストレージ社 半導体開発センター副センター長 矢野和男 (株)日立製作所中央研究所 主管研究長 高山浩一郎 (株)富士通研究所 主管研究員

#### Thanks to Kazunori Tsujimoto and all the members of JST administrative staff.

辻本和典氏始めJSTの担当スタッフの方々に感謝申し上げます。

For more details, please visit the URL:

http://www.dvlsi.jst.go.jp/

http://www.dvlsi.jst.go.jp/english/index.html

14