# 故障注入解析を用いた**VLSI**メモリのディペンダビィティ検証

2010/10/2

株日立製作所 中央研究所 於保 茂

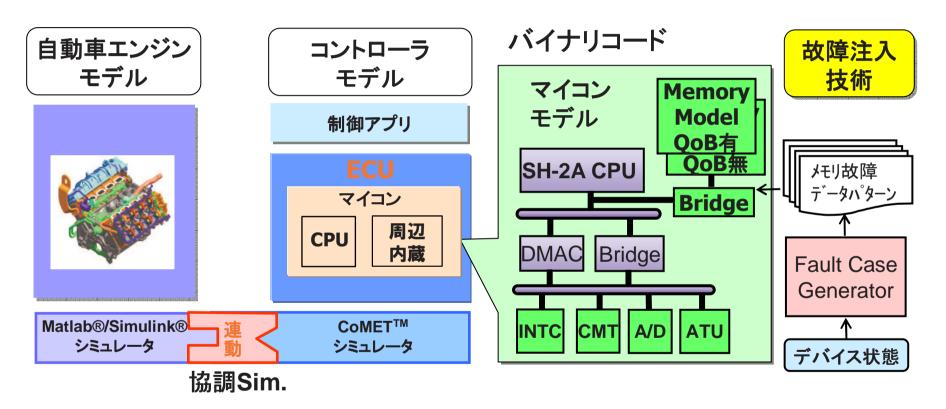

#### 垂直統合型システム検証

◆CPUモデルベースのハードウェア/ソフトウェア協調シミュレーション (Virtualization)による、故障注入技術を組み込んだ検証環境を構築

※Matlab/Simulink: Mathworks社市販のメカ系シミュレータ

CoMET: Synopsys社市販のCPUシミュレータ ECU: Electronic Control Unit (電子制御ユニット) **Model-Based Development**

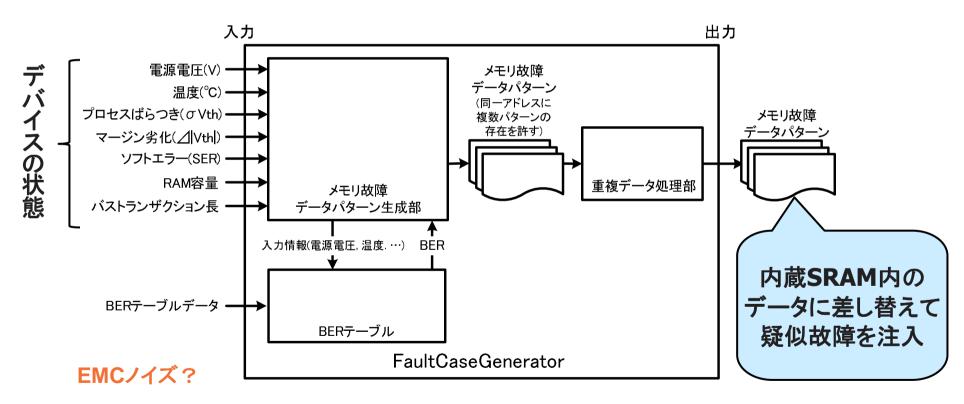

## Fault Case Generator・・・デバイス故障

◆故障モード毎のBER(Bit Error Rate)を算出し、内蔵SRAM内に確率的に疑似故障を発生する Fault Case Generator を実装

Fault Case Generator構成図

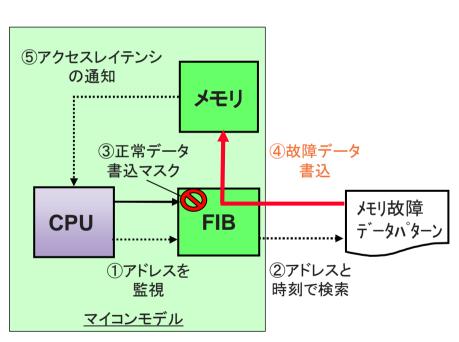

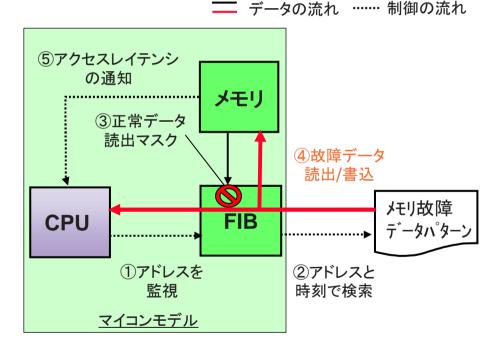

#### デバイス故障の注入

◆Fault Case Generatorから出力された故障データの注入機構(FIB)を、マイコンモデル内CPU−メモリ間バス上に開発し、疑似故障発生を実現 ※FIB (Fault Injectable Bus-bridge)

Writeマージン不良注入方法

Readマージン不良注入方法

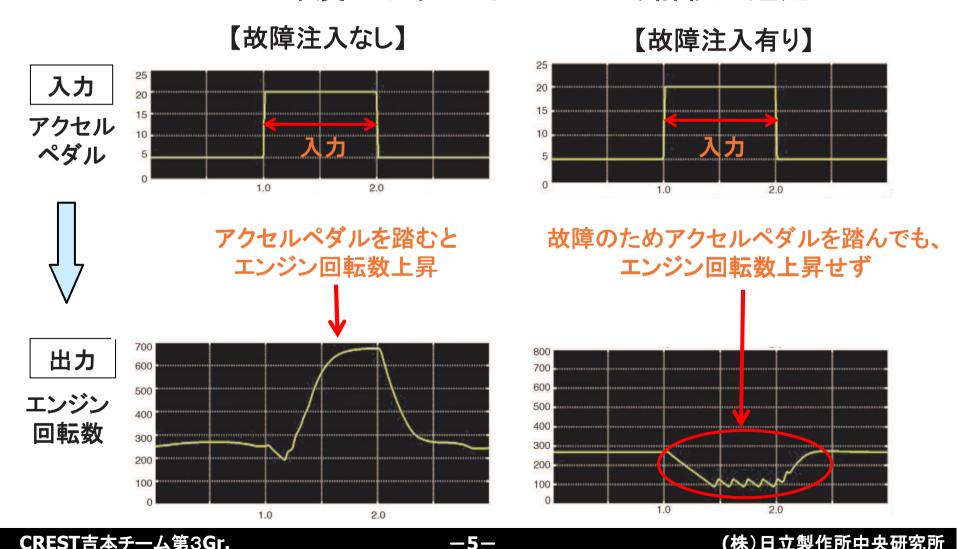

## デバイス故障のシステム影響

◆故障注入の有無が自動車制御システムに与える影響を解析 →H22年度のディペンダブルメモリ評価に適用