# 商用システムに搭載可能な オンチップネットワーク

米田友洋

国立情報学研究所

#### 背景

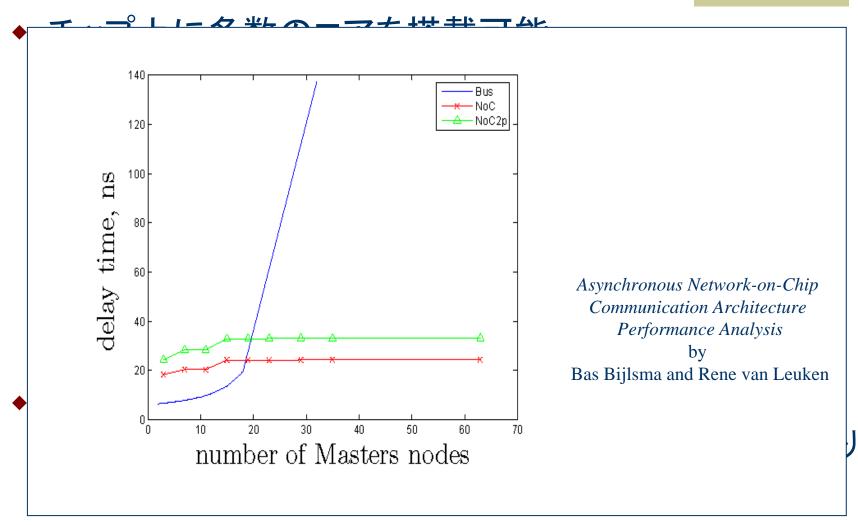

- ◆ チップ上に多数のコアを搭載可能

- 同期式バスアーキテクチャ

- スケーラビリティに問題

- 長配線の容量・抵抗による伝送速度低下

- NoC(Network on Chip)アーキテクチャ

- スケーラビリティの良さ

- 短いリンク上で高速伝送

- 電力消費に対するスループット大

- 同期式NoCの問題点

- グローバルクロック配布の難しさ(単一クロック方式)

- 各ルータにおける再同期化コスト(マルチクロック方式)

- ◆ 非同期式NoCの優位性大

- GALS(Globally Asynchronous Locally Synchronous)により 同期式コアと完全非同期式オンチップネットワーク

# 背景

# 完全非同期オンチップネットワーク

- ◆ 商用システムに搭載するには何が必要か?

- 高性能(高スループット)

- 低消費電力

- ■耐故障性

- ●固定故障

- トランジェント故障

- ■テスト容易性

- 設計容易性

- 標準的インターフェース

#### LETIONOC [DATE2010]

- ◆ 方式: 4相式 QDI(Quasi Delay Insensitive)

- リンクは4線式、ルータは2線式

- 休止相によるオーバヘッドあり

- ◆ 性能: 550Mflit/s(65nm, ルータ単体)

- ◆ 消費電力: 11.9mW/router (同期式に対し86%減)

- ◆ 耐故障性: 特に考慮せず?

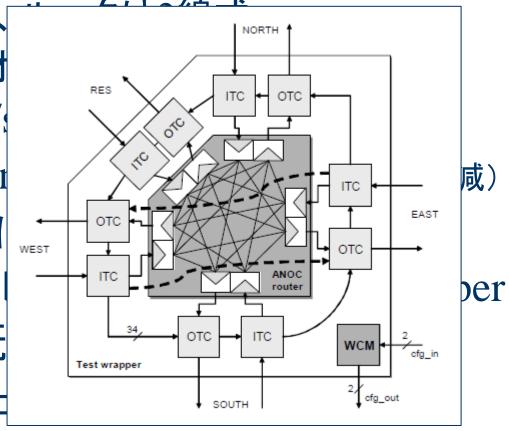

- ◆ テスト容易性: ルータを取り囲むtest wrapper

- ◆ 設計容易性: 既存の同期式CADを駆使

- ◆ 標準インターフェース: 独自仕様

# LETIONOC [DATE2010]

- ◆ 方式:4相式•QDI(Quasi Delay Insensitive)

- リンクは4線式、

- ・休止相によるオ

- ◆ 性能: 550Mflit/s

- ◆ 消費電力: 11.91

- ◆ 耐故障性: 特/

- ◆ テスト容易性: 川

- ◆ 設計容易性: 既

- ◆標準インターフ:

# 本研究での目標

- ◆ 方式:2相式・遅延値制約付き

- リンクは2色2線式、ルータは東データ方式

- 休止相によるオーバヘッドなし

- ◆ 耐故障性:

- 固定故障:単一ルータ・リンク故障回避

- ディペンダブル・アダプティブルーティングアルゴリズム

- ▶トランジェント故障:制御部2重化により同期式と同程 度以上

- ◆ テスト容易性:C素子・FFによるスキャン設計

- ◆ 設計容易性:支援ツールを開発中

- ◆標準インターフェース: OCP(ハード), MCAP(ソフト)等を検討中

# 実証•出口戦略

- ◆ 現在までの成果

- 2×2のプロトタイプ試作: 所望の動作を確認

- ハイブリッド車動力制御ECUの高位モデル作成

- ◆ 実証計画

- 4×4のNoCとしてチップ製作

- HILS(Hardware In the Loop Simulator)システムと上 記アプリにより、下記を実証

- 性能(リアルタイム性)

- 耐故障性

- ◆ 出口戦略

- カーメーカへの売り込み