# ロバストファブリックを用いたディペンダブルVLSIプラットフォーム

研究代表者 京都大学 小野寺秀俊

# 研究の背景

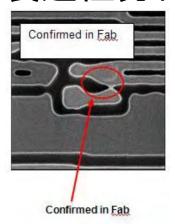

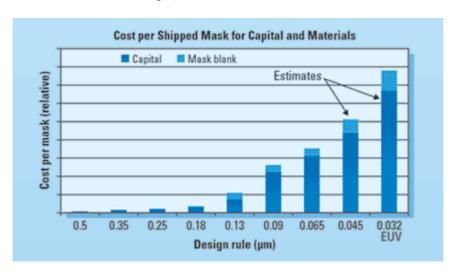

#### ■ 製造性劣化

source: Synopsys

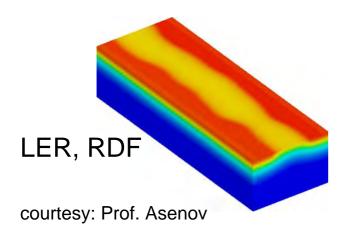

#### ■ 物理的揺らぎ

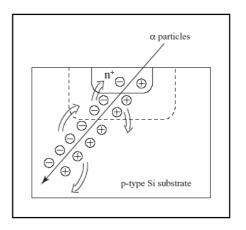

#### ■ 一過性雑音

source: Sanyo

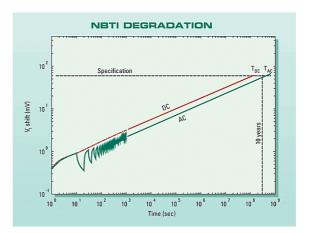

## ■ 特性劣化

**NBTI**

ΔTd ~ 10%@10Ys

Source: Semiconductor International, 2004-03

## 研究背景

## ■ NREコスト急増

Source: Semiconductor International, 2005-09

- ディペンダビリティを毀損する物理的、自然現象的フォールトを排除する素子/回路/アーキテクチャ/設計技術への強い要請

- 同一のチップで、要求されるディペンダビリティの異なる多様なアプリケーションを実現する技術への強い要請

## 研究目的

- 32nm世代以降の不良デバイスが多数出現する VLSIチップ上においても、65nm世代の組み込み 機器が有していたディペンダビリティを確保(具体的目標値は後述)

- より高い信頼性が要求されるアプリに対して高い ソフトエラー耐性を確保

要求されるディペンダビリティに応じた 回路を実現できる再構成可能VLSIプ ラットフォーム

## 解決手段

- 再構成可能ディペンダブルVLSIプラット フォーム

- 要求されるディペンダビリティに応じた回路を 実現

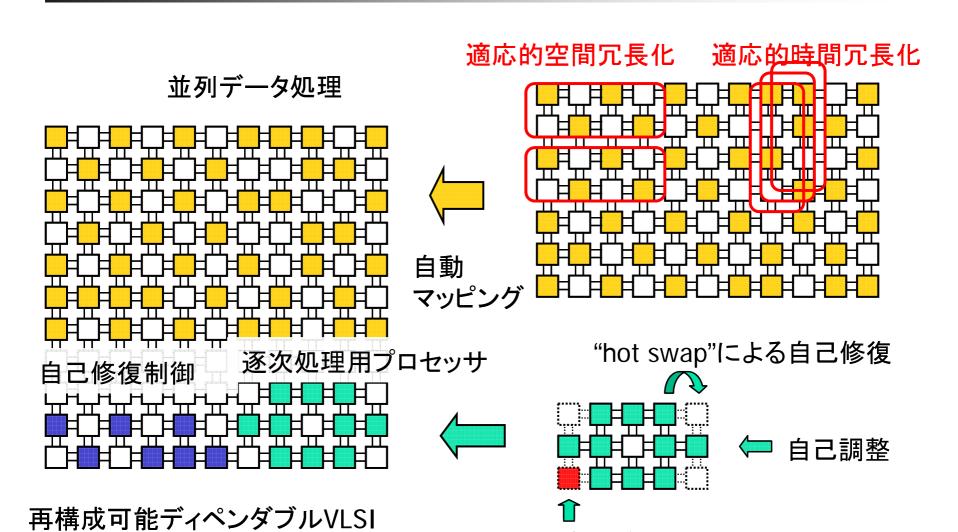

- アーキテクチャ: 適応的な時間的/空間的冗長化

- 回路: ばらつきに強靭な構造、特性の適応的調整

■ 製造性劣化、物理的揺らぎ、ソフトエラー、 特性劣化、NREコストの課題を解決

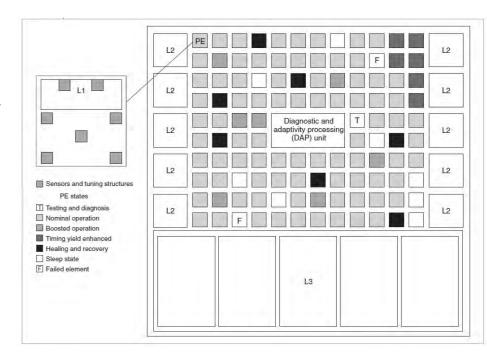

# 提案VLSIプラットフォームのコンセプト

ロバスト(耐ばらつき、高製造性)ファブリックアレイ

自己診断

## 具体的目標

- 製造性劣化、物理的揺らぎ

- ロバストファブリックによりばら つき量を半減

- 一過性雑音

- 適応的な冗長性組み込みにより、宇宙空間でも100FIT達成

- 特性劣化

- 自己調整と自己修復(ホットス ワップ)により動作寿命の2倍化

| ディペンダビリティ阻害要因 |              | 製造性劣化  | 物理的揺らぎ | 一過性雑音  | 特性劣化 |

|---------------|--------------|--------|--------|--------|------|

| 階層            | 技術要素         |        |        |        |      |

| ソフトウェア        | _            |        |        |        |      |

| アーキテクチャ       | 再構成可能アーキテクチャ |        |        | 0      | 0    |

| プロセッサ         | 再構成可能プロセッサ   |        |        | 0      | 0    |

| 設計自動化         | マッピング技術      |        |        | 0      | 0    |

| 回路技術          | ロバストファブリック   | 0      | 0      |        | 0    |

| デバイス技術        | _            |        |        |        |      |

| 阻害要因排除手法      |              | 製造容易構造 | 自己調整   | 適応的冗長化 | 自己修復 |

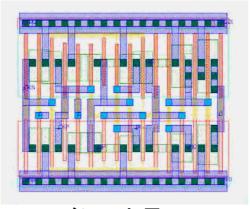

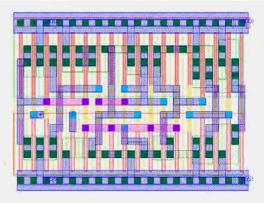

## ロバストファブリック

- 種類

- 論理ファブリック(LUT, ALUなど)

- メモリファブリック

- 配線ファブリック

- 規則性導入による製造性・ばらつき耐性向上

- 改善量とコストの最適なバランス

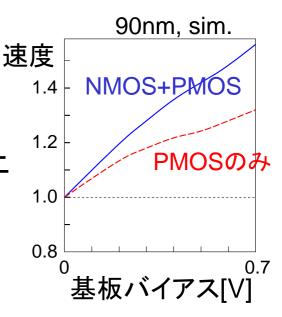

- 特性の自己調整機能

- 細粒度の基板バイアスディザリング

- 65nm D-FF

- ばらつき量 6.8 %

- ▶ ばらつき量 2.7 %

- 14% 面積増加

- ばらつき量 1.3 %

- 29% 面積増加

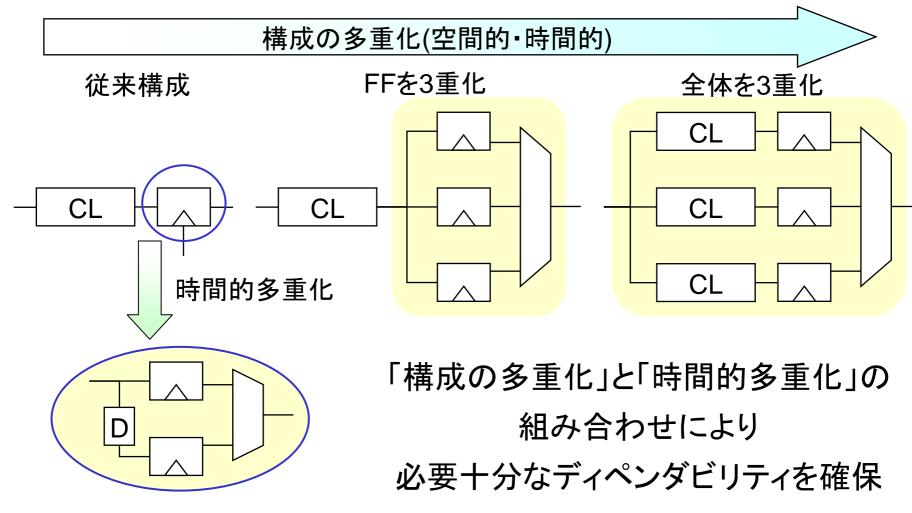

## 適応的多重化によるディペンダビリティ向上

必要とされるディペンダビリティに応じた冗長化構成

CL=Combinational Logic (組み合わせ論理回路)

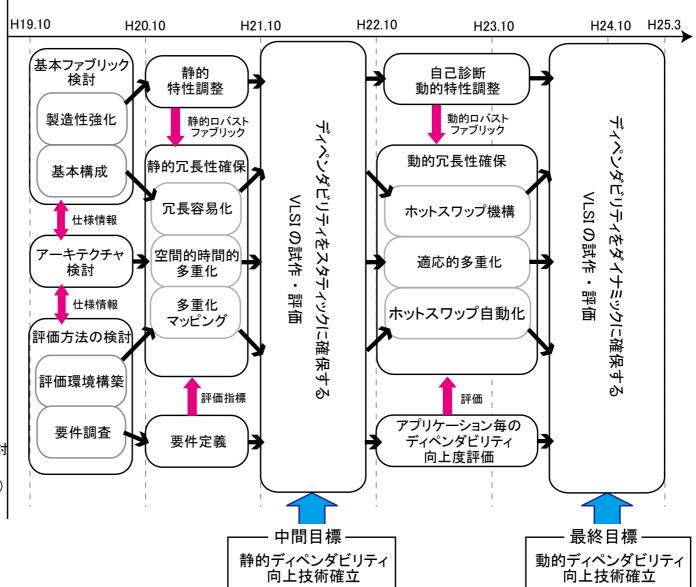

## 研究計画と分担

研究統括 小野寺(京大)

ロバストファブリック 小野寺・土谷 (京大)

再構成アーキテクチャ 尾上・橋本・密山 (阪大)

再構成プロセッサ 小林・嶋田 (京大)

マッピング技術 越智 (京大)

アプリケーション展開に 向けた評価・実用化検討 神原 (京都高度技術研究所)

## マイルストーン

- 中間目標(H22.10)

- 静的ディペンダビリティ向上技術確立

- 最終目標(H25.3)

- 動的ディペンダビリティ向上技術確立

- 検証方法

- 宇宙空間で利用できる暗号化LSIの試作・評価

- 衛星内で必要となる回路の例: 圧縮回路、暗号回路、GPS用相 関器回路、通信プロトコル関係回路など

- JAXA 総合技術研究本部 部品・材料・機構技術グループ(技術領域リーダ: 久保山智司殿)と協議中

- 様々なディペンダビリティが実現できることを確認

- 他の実証例題も検討予定(通信、運輸分野など)

## 研究体制

- 研究統括 小野寺秀俊(京都大学)

- ロバストファブリック

- 小野寺秀俊、土谷亮 (研究代表者グループ 1)

- 再構成アーキテクチャ

- ■尾上孝雄、橋本昌宜、密山幸男 (大阪大学)

- 再構成プロセッサ

- 小林和淑、嶋田創 (研究代表者グループ2)

- ■マッピング技術

- 越智裕之 (研究代表者グループ 3)

- アプリケーション展開と評価・実用化検討

- ■神原弘之 (京都高度技術研究所)

# 研究代表者グループ

## ロバストファブリック

#### 小野寺秀俊

- 製造容易化設計技術の先駆的研究

- 実績:

- 2007 VLSI Technology Symp.(招待講演)

- IEICE Trans. Electron. 2006/3.(招待論文)

- 2005 IWFIPT (招待講演/パネリスト)

### 土谷亮

- オンチップ配線のエキスパート

- 実績:

- ASP-DAC2004 Best Paper Award

- MWE 2007 招待講演

## 再構成プロセッサ

#### 小林和淑

- LSI設計分野を牽引する若手教員

- 実績:

- Resource-Shared VLIW Processor

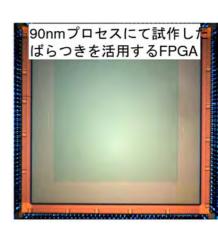

- ばらつきを活用するFPGA(世界初)

#### 嶋田創

- プロセッサアーキテクチャのエキスパート

- 実績:

- 可変段数パイプラインによる消費電力削減

## ■ マッピング技術

#### 越智裕之

- 再構成アーキテクチャの第一人者

- 実績

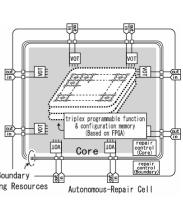

- 再構成デバイスの設計自動化環境構築<sup>®oundary</sup> —

- 再構成デバイスの耐故障化(宇宙利用可能)

# 共同研究者グループ(大阪大学)

## 再構成アーキテクチャ

#### 尾上孝雄

- メディア処理用ハードウェアアーキテクチャ研究で世界的なリーダーシップ

- 実績:

- ISO/IEC SC29/WG1(JPEG)委員としてシステム実装可能性の面から標準化に尽力

#### 橋本昌宜

- ばらつき考慮設計技術の第一人者

- 実績:

- 製造・環境ばらつきを考慮したタイミング解析を実現

- システムLSI WS 招待講演(2004, 2007)

#### 密山幸男

- 再構成アーキテクチャのエキスパート

- 実績

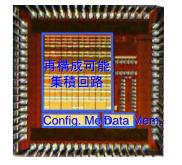

- メディア処理向け再構成可能LSIの開発

- 再構成デバイスを用いた暗号処理方式の開発

# 共同研究者グループ(京都高度技術研究所)

■ アプリケーション展開に向けた評価 • 実用化検討

#### 神原弘之

- プロセッサ、高位合成に加えて各種アプリケーション(AES 暗号化)に精通

- ハードとソフトの双方を熟知

- 実績(大学等との共同研究とその実用化)

- 教育用プロセッサの研究開発と頒布

- UDL/I 言語の仕様策定その処理系開発

- ソフトコアプロセッサの研究開発(九州大学と共同)と 着メロIP としての実用化

# 10月9日プロジェクト会議(阪大にて)

## 独創性•新規性

■回路技術、再構成可能アーキテクチャ技術、 設計自動化技術の総合的取り組みにより多 様な(必要十分な)ディペンダビリティを確保

- ■類似研究

- ミシガン大: ElastIC

- プロセッサアレー

- ■適用範囲限定的

IEEE Design & Test 2005-11/12

# 初年度の研究計画と成果目標

- ロバストファブリック

- 規則性導入による製造性向上とコストのトレードオフ解析を行い、ばらつき量半減のエビデンス獲得

- 基板電圧の選択的印加による特性ばらつき/劣化補償法のフィージビリティを明確化

- 再構成アーキテクチャ

- 冗長化容易な再構成デバイス基本セルアーキテクチャの明確化

- 再構成プロセッサ

- 冗長化容易なプロセッサ基本構成の明確化

- マッピング技術

- 評価環境の構築(マッピング、シミュレーション、静的多重化支援)

- アプリケーション展開

- VLSIユーザへのヒアリングに基づく信頼性の要件調査

# 将来展望

- ディペンダビリティ要件に応じて再構成可能な VLSIプラットフォーム

- 物理的・自然的フォールトを克服

- ■学術領域への波及効果

- デバイスの完全動作を前提としない新たな設計 パラダイムの創出

- ■半導体産業への波及効果

- 信頼性を新たな付加価値としたVLSIシステムの 提供による新規領域(マーケット)の開拓

- ネットワーク化社会への波及効果

- 基幹部品である半導体システムの信頼性・安全性を確保