## Dependable Memory Techniques for Highly Reliable VLSI System

JST/CREST/DVLSI Symposium, Dec. 1, 2012

Masahiko Yoshimoto, Kobe Univ. Hiroshi Kawaguchi, Kobe Univ. Makoto Nagata, Kobe Univ. Koji Nii, Renesas Electronics Shigeru Oho, Nippon Institute of Technology Yasuo Sugure, Hitachi, Ltd.

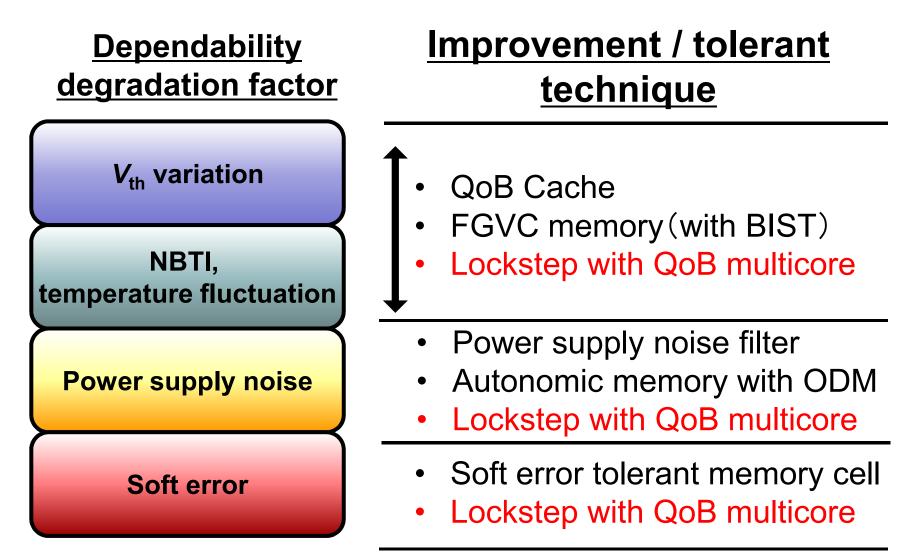

# **Dependability degradation factor**

QoB: Quality of Bit FGVC: Fine-Grain Voltage Control

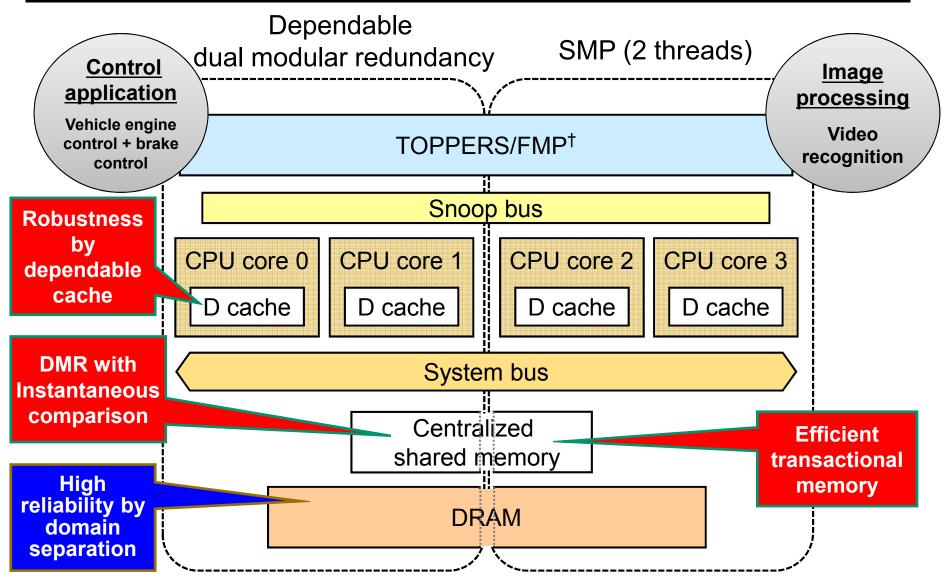

## Dependable QoB multicore processor system

† TOPPERS/FMP: new generation kernels - to provide support for multi-core processors. Both symmetric and asymmetric configurations are supported by TOPPERS project.

3

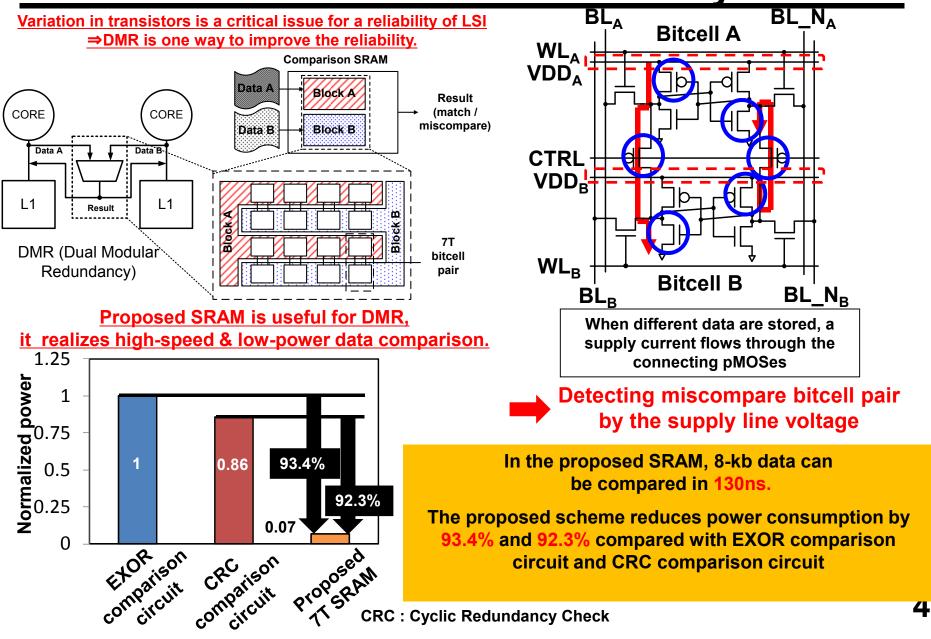

### Instantaneous Block data comparison (QoB) for Dual Modular Redundancy

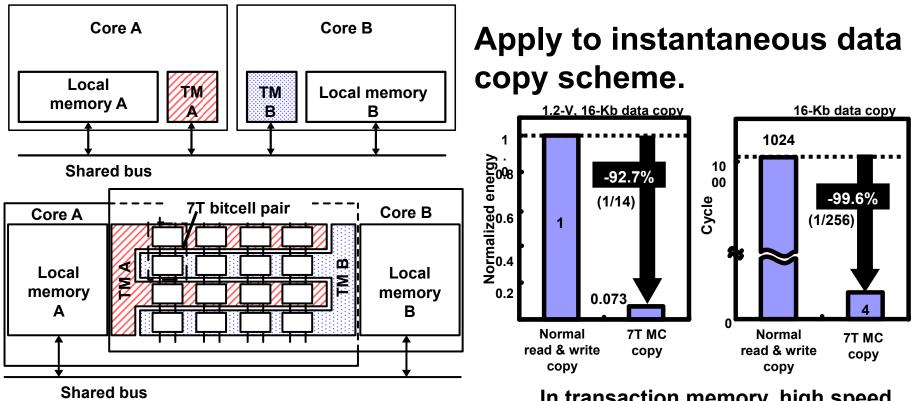

# Instantaneous Block data copy (QoB) for Transaction memory

#### **Transaction Memory at multicore processor**

(a) general case and (b) copiable 7T SRAM architecture for transactional memory

In transaction memory, high speed recovery without shared bus is realized.

Data copy energy is saved 92.7%. Copy cycle is saved by 99.6%.

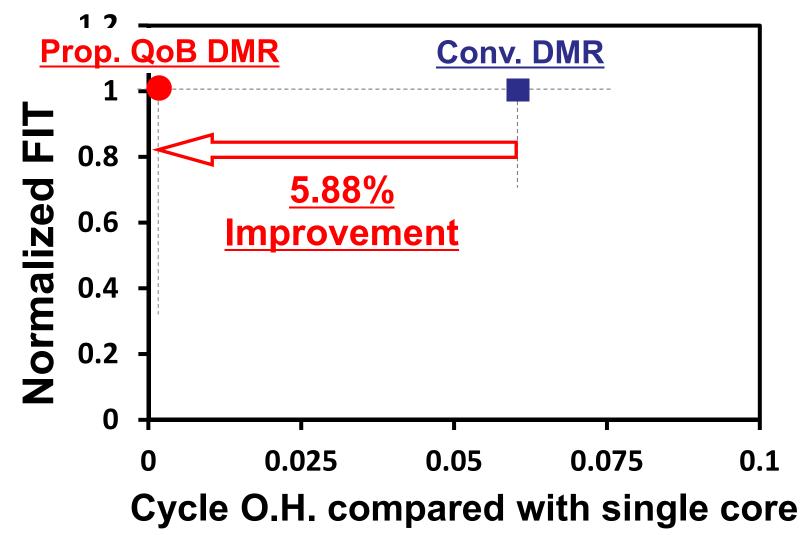

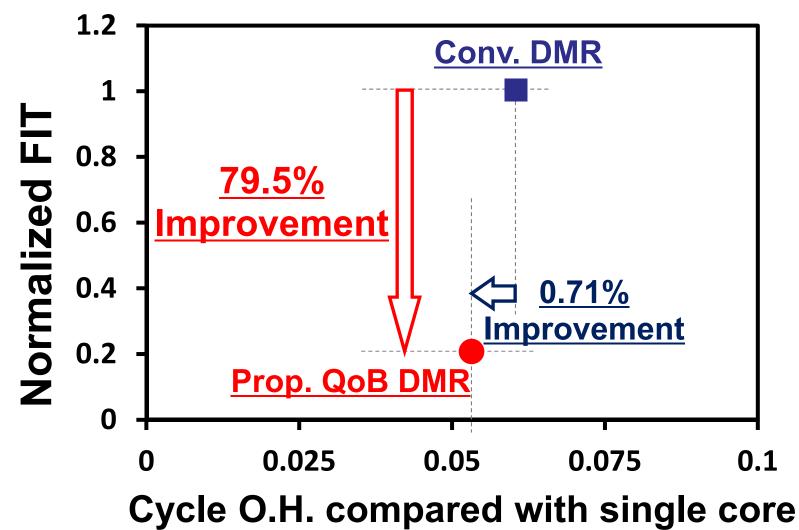

## FIT and cycle O.H. improvement of QoB DMR

## FIT and cycle O.H. improvement of QoB DMR