### 車載制御用ディペンダブル ネットワークオンチップIP

「ディペンダブルネットワークオンチッププラットフォームの構築」 戦略的創造研究推進事業 「ディペンダブルVLSIシステムの基盤技術」

研究代表者 米田友洋(国立情報学研究所) 主たる共同研究者 今井 雅(東京大学) 松本 敦(東北大学) 齋藤 寛(会津大学)

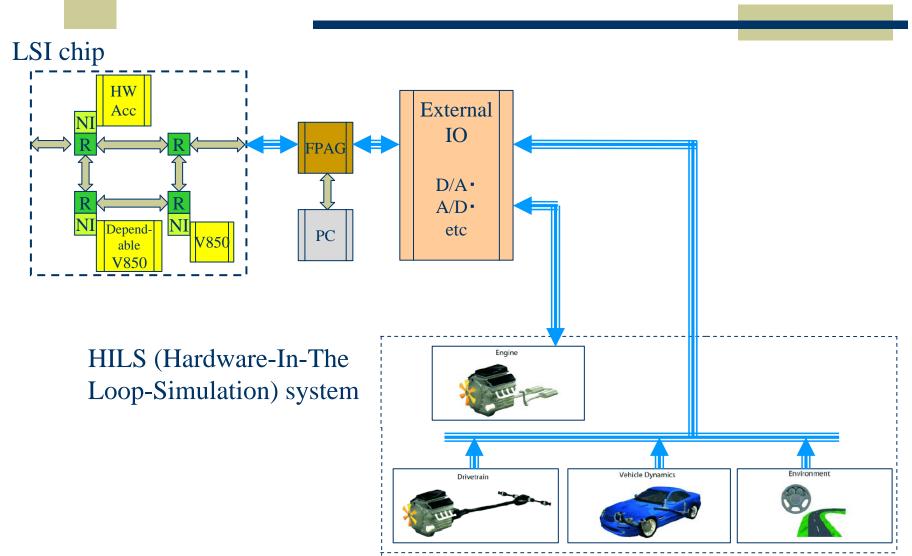

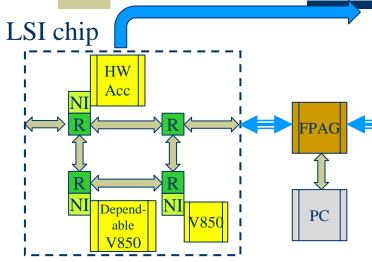

HILS (Hardware-In-The Loop-Simulation) system

## 第二次実証用モデル

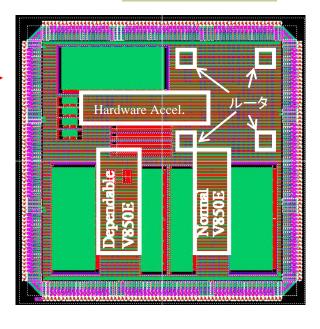

- ◆ ディペンダブルなオンチップネットワーク

- 非同期式実現による耐劣化性

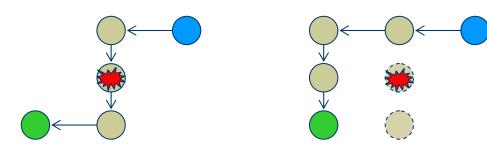

- 故障ルータを自律的に避けてパケットを伝送するディペンダブルルーティング

- 符号化リンクに適した新しいタイムアウト検出手法(特 許出願)

- ソフトエラー等への耐性を高めた制御回路構成法

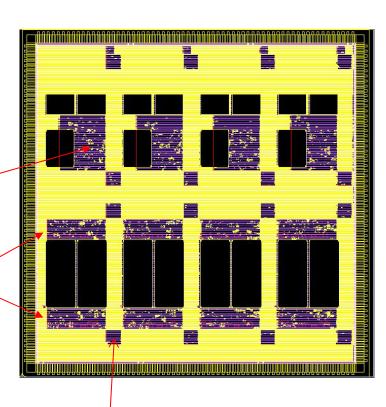

## 第二次実証用モデル

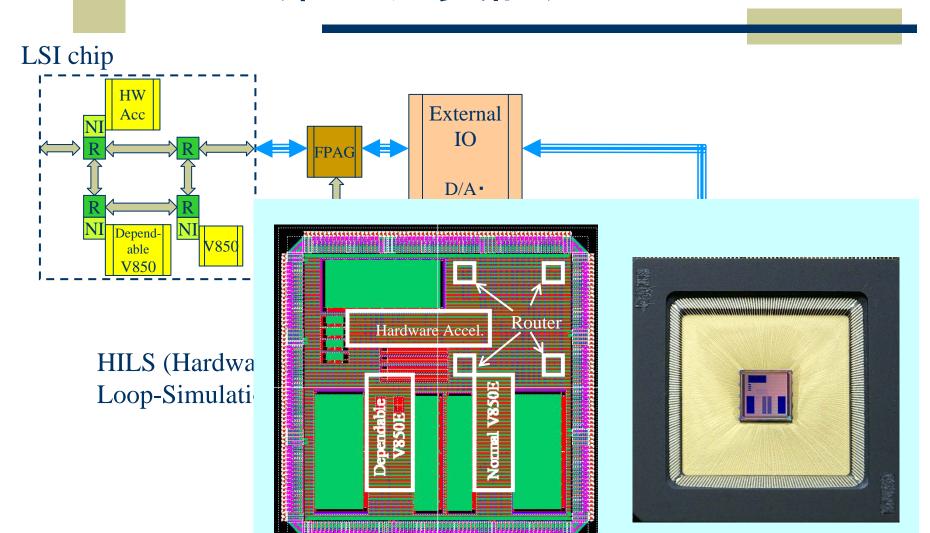

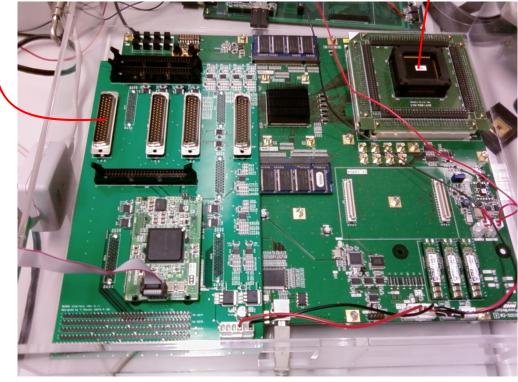

◆ これらの一部をチップとして実現し、12/15に

テープアウト

来年度実証用

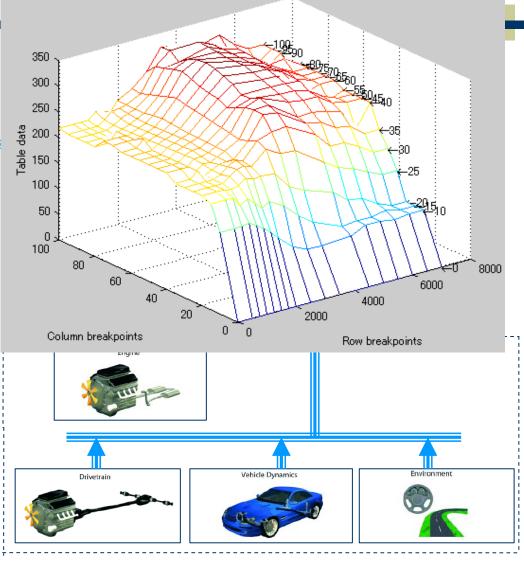

浮動小数点テーブル 補間アクセラレータ つ コア4個

> V850E CPUコア 8個

非同期ルータ 16個(4×4メッシュ)

# 非同期式回路用遅延値決定支援 ツール

「ディペンダブルネットワークオンチッププラットフォームの構築」 戦略的創造研究推進事業 「ディペンダブルVLSIシステムの基盤技術」

研究代表者 米田友洋(国立情報学研究所) 主たる共同研究者 今井 雅(東京大学) 松本 敦(東北大学) 齋藤 寛(会津大学)

### 目的

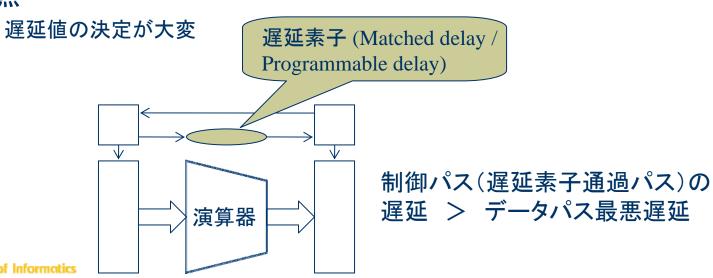

- ◆ 東データ方式の非同期式回路

- 演算器毎に遅延素子により遅延をマッチさせる

- 利点

- ◆ 同期式回路のデータパス回路が使用可能

- 演算器毎に遅延を最適化できる

- ◆ プログラマブル遅延素子を使えば、静的・動的遅延変動にも対応可

- 欠点

### 目的

- ◆ 東データ方式の非同期式回路

- 演算器毎に遅延素子により遅延をマッチさせる

- 利点

- ◆ 同期式回路のデータパス回路が使用可能

- 演算器毎に遅延を最適化できる

- プログラマブル遅延素子を使えば、静的・動的遅延変動にも対応可

- 欠点

- 遅延値の決定が大変

- ◆ 遅延値の決定を支援するツールが必要

- 現段階ではコアアルゴリズムの開発まで

- 効率・ユーザインタフェースの改善は来年度以降

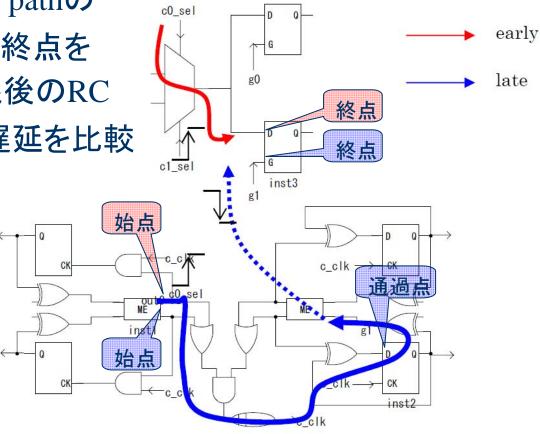

## 方式

- ◆ 遅延制約:(制御パス遅延)>(データパス遅延)

- Early path, Late pathの 始点、(通過点)、終点を 指定し、配置配線後のRC 情報を基にパス遅延を比較

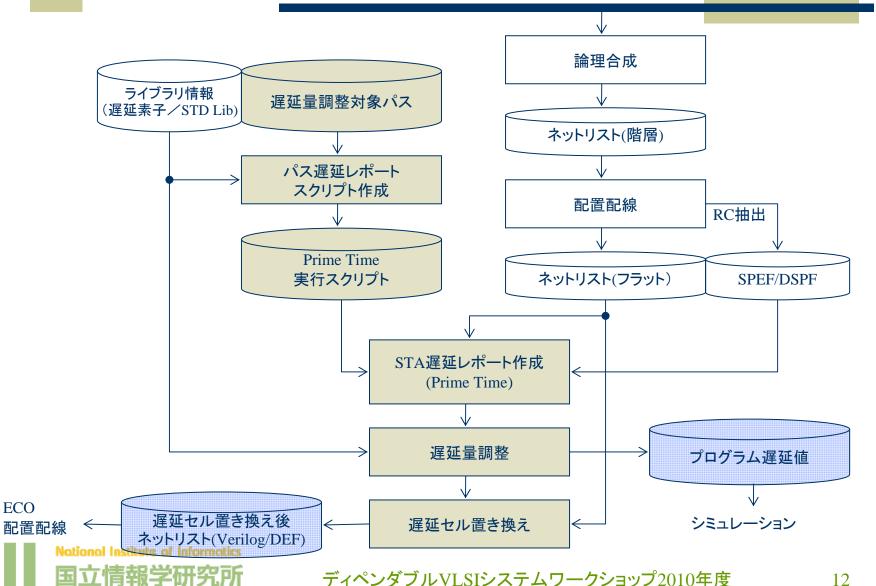

## 処理フロー

**ECO**