#### CREST 「ディペンダブルVLSIシステムの基盤技術」 領域会議資料

# 「超高信頼性VLSIシステムのためのディペンダブルメモリ技術」

平成20年10月27日 吉本チーム

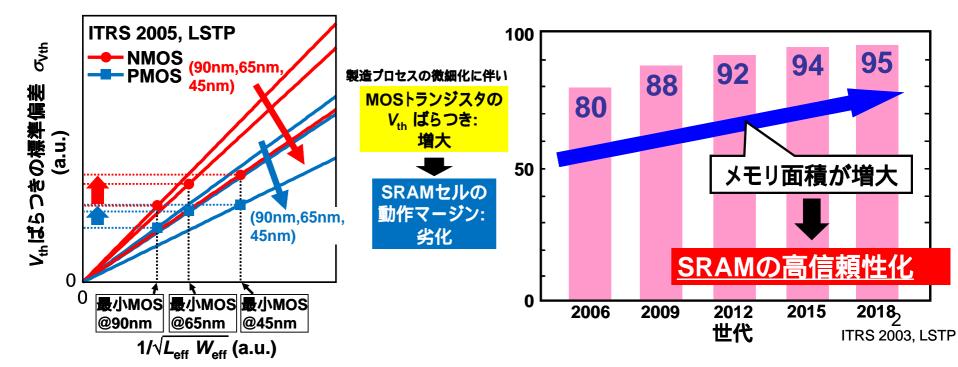

## 研究背景

- 微細化·大規模化·高性能化が進むLSIでは、物理的エラー·人為的エラーを 完全には排除できない

- 速度・電圧・温度・入出力信号の品質などのあらゆる外部環境を満足して動作するLSIはもはや実現不可能になる

- また、アプリケーションによって要求される信頼性が異なる

- LSIの動作マージンは組み込みSRAMが支配

## 研究内容

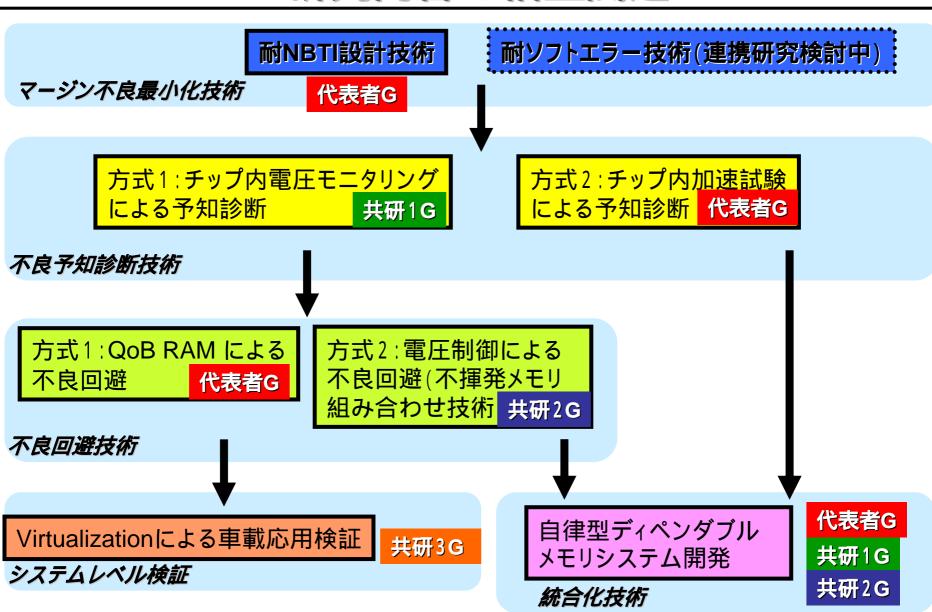

ディペンダブルメモリに関する3要素設計技術と統合化技術

極力マージン不良を出さない新しい設計技術を開発する。

実時間オンチップモニタリング技術や実使用時の加速試験 などによる<u>不良予知診断技術</u>を開発する。

外部環境の変化があっても高信頼性を維持し動作し続けられる新しい<u>不良回避技術</u>を開発する。

上記3要素技術を統合化し、<u>自律型ディペンダブルメモリ</u> <u>システム</u>を開発する。

提案する高ディペンダブルメモリシステムの<u>実応用での</u> 有用性について検証する。

## 研究内容の相互関連

## 不良予知診断

予知方法1:チップ内電圧モニタリングによる予知診断

- ・高精度なオンチップモニタリング回路の内蔵

- ・ブロック毎に測定データのログを更新

- ・取得データのチップ内統計解析による予知診断

予知方法2:チップ内加速試験による予知診断

- ・実使用状態で空きブロックの加速試験

- ・フレキシブル電源ネットワークを利用

## 不良回避技術

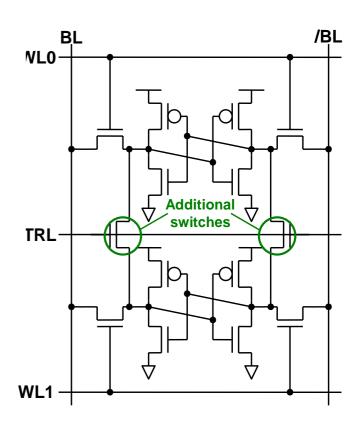

回避方法1:QoB (Quality of Bit) RAMによる不良回避

- ·動作環境が劣化した場合、動作継続可能 (Sustainable)な構成にスイッチする。

- ·高信頼度要求時には動作マージンのある構成にスイッチする。

- ・QoB RAM を制御するミドルウエア、OS

回避方法2:細粒度電圧制御による不良回避 (不揮発メモリによるプログラミング)

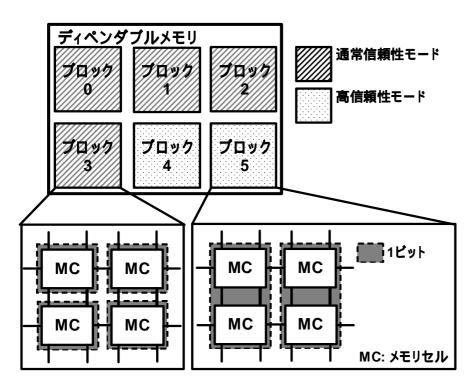

## 回避方法1:QoBメモリ(構成)

高信頼性モードでは、1ビットの情報を2つのメモリセルで保持する。

低電圧動作や高速動作などの信頼性要素をブロック毎にスケーラブルに制御できる。

H.Fijiwara, et al, "Quality of a Bit (QoB): A New Concept in Dependable SRAM", ISQED2008にて発表。

# 回避方法1:QoBメモリ(応用)

メモリマクロの外部環境の悪化(電源変動、電源低下、温度変化など)あるいは内部特性の経時変化(NBTIなど)に対応して、構成を切り替える。

- 通常動作条件では7T構成を割り当てる。

- マージンが不足すると、14T構成を割り当てる。

#### 求められる信頼性に応じて構成を切り替える(銀行ATMの例)

- ATMの画面には信頼性とは直接の関係がない、広告の列 挙やアニメーションなどのGUIがある。

- これには7Tメモリセルを割り当てる

- 金額のサーバー間通信や暗号化は信頼性が要求される

- 14Tを割り当てる

#### 動的な信頼性変更はミドルウエアまたはOSにより制御

## 統合化実装技術

ディペンダブルメモリシステムのハードウエアプラットフォームとなるフレキシブル電源ネットワークの開発 (フラッシュ混載プロセスを使用)

上記を用いた自律型不良回避メモリシステムの開発

## 実応用での有用性検証

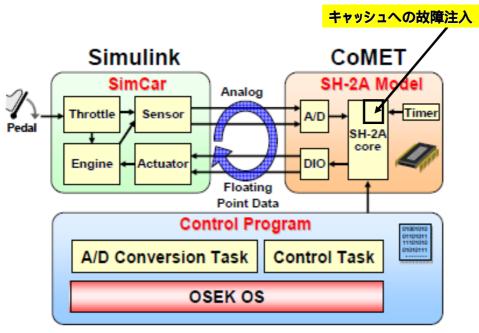

エンジンコントロールなど実システムでの動作シミュレーション (日立中研発表の論文(Makoto Ishikawa, D.J.McCune, George Saikalis, Shigeru Oho, "CPU Model-Based Mechatronics/Hardware/Software Co-design Technology for Real-Time Embedded Control System" IEICE Trans. Electron., vol. E90-C, no. 10,

pp. 1992-2001, Oct. 2007.) から抜粋)

#### <u>Virtualization技術による検証</u>

- ・プロセッサコア内部のキャッシュへの故障注入

- ・仮想システムによる有用性検証

- ・車載応用(エンジン制御)

- ·エンジン制御性能への信頼性(BER)の影響評価

#### 想定応用

- ·車載

- エンジン制御

- ABS

- クルーズコントロール

- 安全·安心システム 運転支援 危険予知 障害物検知 標識認知

- ・ネットワーク - ルータチップ

# 研究体制

| グループ名               | 研究代表者又は 主た<br>る共同研究者氏<br>名 <sup>1)</sup> | 所属機関·部署·役職名 <sup>2)</sup>                          | 研究題目3)                                                            |

|---------------------|------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|

| 代表者グループ             | 吉本 雅彦 川口 博                               | 神戸大学工学研究科·<br>情報知能学専攻·教授<br>情報知能学専攻·准教授            | マージン不良最少化 技術、不良予知診断、不良回避技術 および統合化システムの開発                          |

| 共同研究グ<br>ループ<br>(1) | 永田 真                                     | 神戸大学工学研究科·<br>情報知能学専攻·准教授                          | チップ内モニタリング<br>による不良予知診<br>断技術の開発                                  |

| 共同研究グ<br>ループ<br>(2) | 篠原 尋史                                    | 株式会社ルネサステク/ロジ<br>製品技術本部 設計技術統<br>括部 設計基盤開発部・<br>部長 | 細粒度電圧制御による不良回避技術と<br>ディペンダブルメ<br>モリシステムのハ<br>ードウエアプラット<br>フォームの開発 |

| 共同研究グ<br>ループ<br>(3) | 於保 茂                                     | (株)日立製作所 中央研究所<br>ソリューションLSI研究センタ<br>主管研究員         | システムレベル検証<br>技術の開発<br>11                                          |

# 研究スケジュール

| 研究項目              | 分担                  | H20 | H21                    | H22                | H23    | H24   | H25 |

|-------------------|---------------------|-----|------------------------|--------------------|--------|-------|-----|

| マージン不良<br>最小化技術   | ■ 11. 衣有            |     |                        | 耐NBTI<br>設計技術      |        |       |     |

| 不良予知<br>診断技術      | 共同研究<br>グループ<br>(1) |     | ニップ内<br>ニタリング          | 動作不良の モデリングと エラー予想 | 自律     |       |     |

|                   | 研究<br>代表者<br>グループ   | 둞   | プ内加速<br>験による<br>見予知診断  | システム 実装            | 律メモリシス | 1<br> |     |

| <b>不应同"啦++</b> 4- | 研究<br>代表者<br>グループ   | Q   | B RAM<br>回路            | 他方式との組み合わせ         | ステム    |       |     |

| 不良回避技術            | 共同研究<br>グループ<br>(2) |     | 発メモリ応用<br>スイッチ用ツ       |                    |        | <br>  |     |

| システム<br>レベル検証     | 共同研究<br>グループ<br>(3) |     | 検証環境構築<br>故障注入<br>技術開発 | Virtualiza<br>車載応  | -      |       | 12  |

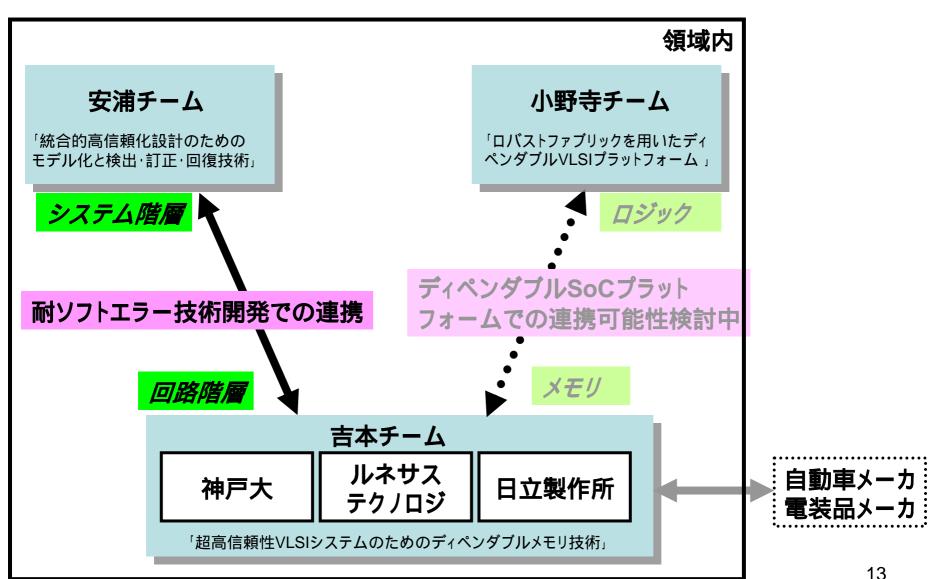

## 領域内チーム間連携と外部連携

## まとめ(マイルストーン)

「1」オンチップモニタリング(SRAM)と フィールドでのBER予知技術

平成22年度

要素技術(予知診断)

「2」SustainableなQ0B(Quality of Bit)RAM

要素技術(不良回避)

平成22年度

「3」フラッシュ混載技術を用いた自律的メモリ不良回避システム *統合技術(ディペンダブルメモリ技術)* 平成23年度

「4」Virtualization技術によるシステムレベル検証 平成23年度